# x86-64 Programming I

CSE 351 Summer 2018

#### **Instructor:**

Justin Hsia

#### **Teaching Assistants:**

Josie Lee Natalie Andreeva

Teagan Horkan

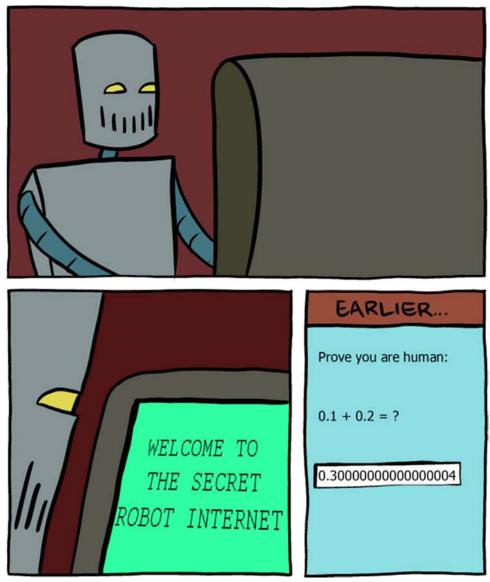

http://www.smbc-comics.com/?id=2999

#### Administrivia

- Lab 1b due on Thursday (7/5)

- Submit bits.c, lab1reflect.txt

- Josie has OH on Thursday 1–3 pm

- Homework 2 due next Wednesday (7/11)

- On Integers, Floating Point, and x86-64

- No lecture on Wednesday!

- Section Thursday on Floating Point

# **Floating Point Summary**

- Floats also suffer from the fixed number of bits available to represent them

- Can get overflow/underflow

- "Gaps" produced in representable numbers means we can lose precision, unlike ints

- Some "simple fractions" have no exact representation (*e.g.* 0.2)

- "Every operation gets a slightly wrong result"

- Floating point arithmetic not associative or distributive

- Mathematically equivalent ways of writing an expression may compute different results

- Never test floating point values for equality!

- Careful when converting between ints and floats!

#### Number Representation Really Matters

- ✤ 1991: Patriot missile targeting error

- clock skew due to conversion from integer to floating point

- \* 1996: Ariane 5 rocket exploded (\$1 billion)

- overflow converting 64-bit floating point to 16-bit integer

- **2000:** Y2K problem

- Iimited (decimal) representation: overflow, wrap-around

- ✤ 2038: Unix epoch rollover

- Unix epoch = seconds since 12am, January 1, 1970

- signed 32-bit integer representation rolls over to TMin in 2038

#### Other related bugs:

- 1982: Vancouver Stock Exchange 10% error in less than 2 years

- 1994: Intel Pentium FDIV (float division) HW bug (\$475 million)

- 1997: USS Yorktown "smart" warship stranded: divide by zero

- 1998: Mars Climate Orbiter crashed: unit mismatch (\$193 million)

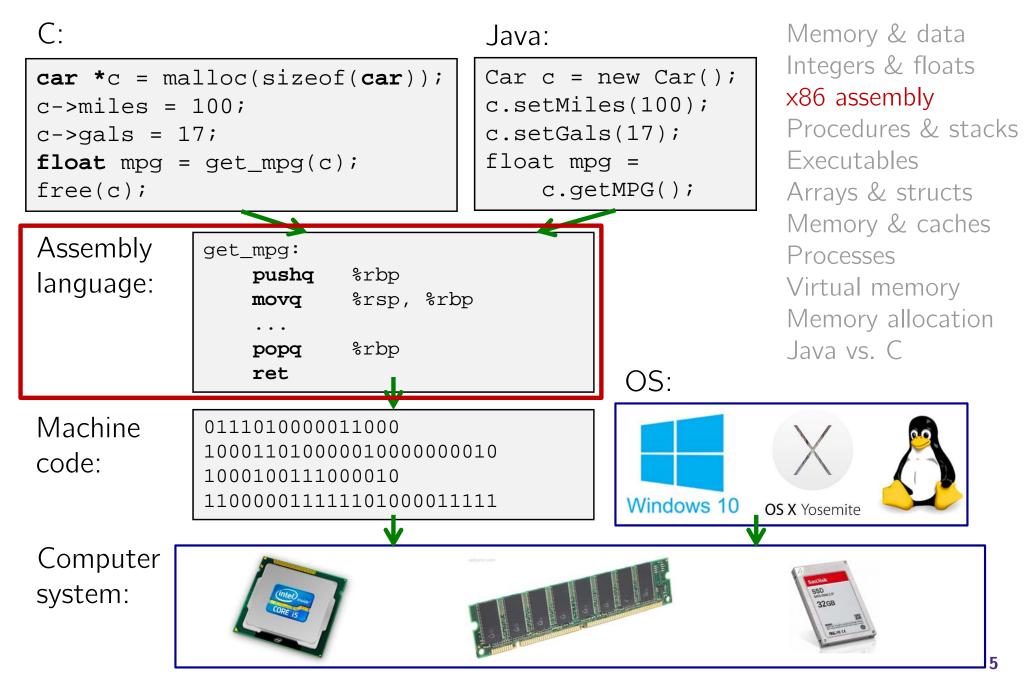

#### Roadmap

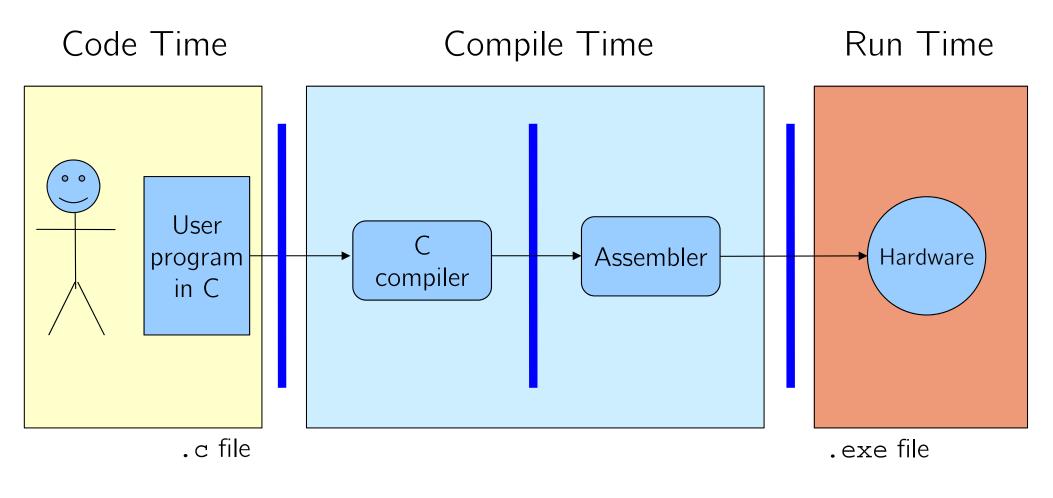

#### Translation

What makes programs run fast(er)?

#### **HW Interface Affects Performance**

#### **Instruction Set Architectures**

- The ISA defines:

- The system's state (*e.g.* registers, memory, program counter)

- The instructions the CPU can execute

- The effect that each of these instructions will have on the system state

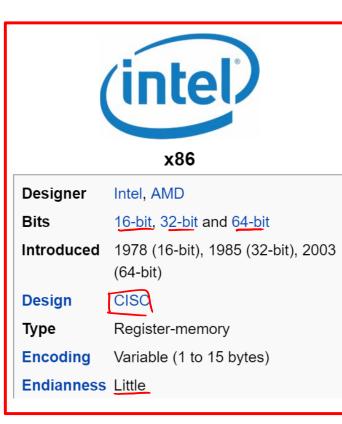

#### **Instruction Set Philosophies**

- Complex Instruction Set Computing (CISC): Add more and more elaborate and specialized instructions as needed

- Lots of tools for programmers to use, but hardware must be able to handle all instructions

- x86-64 is CISC, but only a small subset of instructions encountered with Linux programs

- Reduced Instruction Set Computing (RISC): Keep instruction set small and regular

- Easier to build fast hardware

- Let software do the complicated operations by composing simpler ones

# **General ISA Design Decisions**

#### Instructions

- What instructions are available? What do they do?

- How are they encoded? instructions are data!

binary encoding

- Registers

- How many registers are there?

- How wide are they? word size (64 bits)

- Memory

- How do you specify a memory location?

an address is a word size different ways to specify/"build" an address

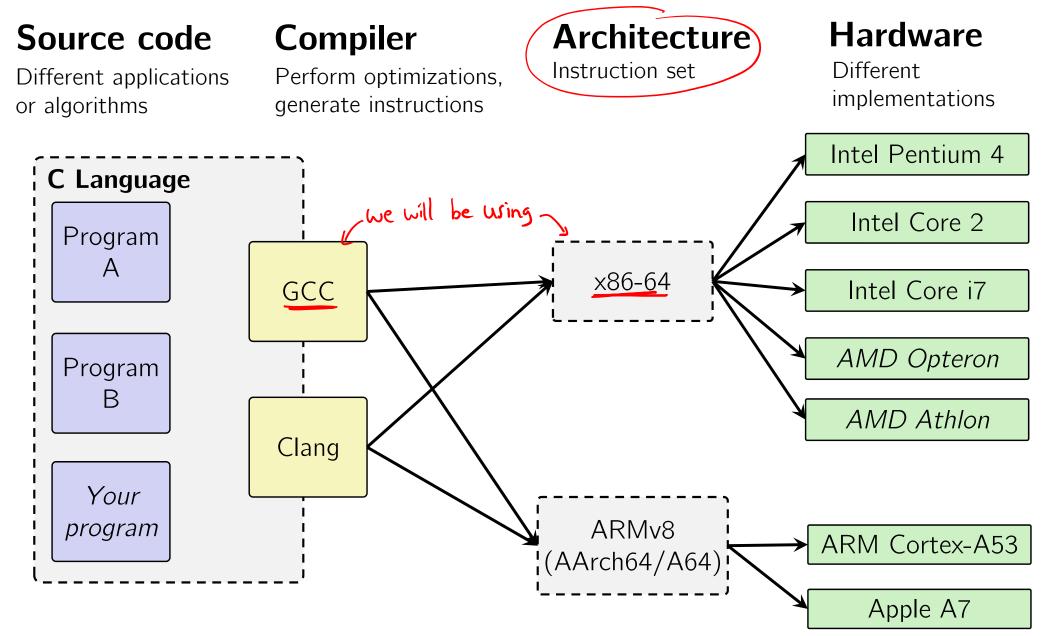

## Mainstream ISAs

Macbooks & PCs (Core i3, i5, i7, M) <u>x86-64 Instruction Set</u>

#### **ARM** architectures

| Designer   | ARM Holdings                                                                                                                                                          |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bits       | 32-bit, 64-bit                                                                                                                                                        |

| Introduced | 1985; 31 years ago                                                                                                                                                    |

| Design     | RISC                                                                                                                                                                  |

| Туре       | Register-Register                                                                                                                                                     |

| Encoding   | AArch64/A64 and AArch32/A32<br>use 32-bit instructions, T32<br>(Thumb-2) uses mixed 16- and<br>32-bit instructions. ARMv7 user-<br>space compatibility <sup>[1]</sup> |

| Endianness | Bi (little as default)                                                                                                                                                |

Smartphone-like devices (iPhone, iPad, Raspberry Pi) <u>ARM Instruction Set</u>

#### MIPS

| MIPS Technologies, Inc. |

|-------------------------|

| <u>64-bit</u> (32→64)   |

| 1981; 35 years ago      |

| RISC                    |

| Register-Register       |

| Fixed                   |

| Bi                      |

|                         |

Digital home & networking equipment (Blu-ray, PlayStation 2) <u>MIPS Instruction Set</u>

#### Definitions

- Architecture (ISA): The parts of a processor design that one needs to understand to write assembly code

- "What is directly visible to software"

- Microarchitecture: Implementation of the architecture

- CSE/EE 469, 470

- Are the following part of the architecture?

- Number of registers? Yes

- How about CPU frequency? No

- Cache size? Memory size? No modul ar

# Writing Assembly Code? In 2018???

- Chances are, you'll never write a program in assembly, but understanding assembly is the key to the machinelevel execution model:

- Behavior of programs in the presence of bugs

- When high-level language model breaks down

- Tuning program performance

- Understand optimizations done/not done by the compiler

- Understanding sources of program inefficiency

- Implementing systems software

- What are the "states" of processes that the OS must manage

- Using special units (timers, I/O co-processors, etc.) inside processor!

- Fighting malicious software

- Distributed software is in binary form

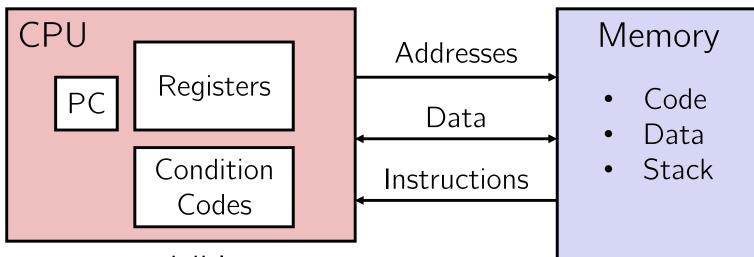

## **Assembly Programmer's View**

- Programmer-visible state

- PC: the Program Counter (%rip in x86-64)

- Address of next instruction

- Named registers

- Together in "register file"

- · Heavily used program data

- Condition codes

- Store status information about most recent arithmetic operation

- Used for conditional branching

- Memory

- Byte-addressable array

- Code and user data

- Includes the Stack (for supporting procedures)

#### x86-64 Assembly "Data Types"

- Integral data of 1, 2, 4, or 8 bytes

- Data values

- Addresses (untyped pointers)

- ✤ Floating point data of 4, 8, or 2x8, 4x4, or 8x2

- Different registers for those (e.g. %xmm1, %ymm2)

- Come from *extensions to x86* (SSE, AVX, ...)

- No aggregate types such as arrays or structures

- Just contiguously allocated bytes in memory

- Two common syntaxes

- "("AT&T": used by our course, slides, textbook, gnu tools, ...

- × "Intel": used by Intel documentation, Intel tools, ...

- Must know which you're reading

#### What is a Register?

- A location in the CPU that stores a small amount of data, which can be accessed very quickly (once every clock cycle)

- ✤ Registers have *names*, not *addresses*

- In assembly, they start with % (e.g. %rsi)

- Registers are at the heart of assembly programming

- They are a precious commodity in all architectures, but especially x86 only 16 of them...

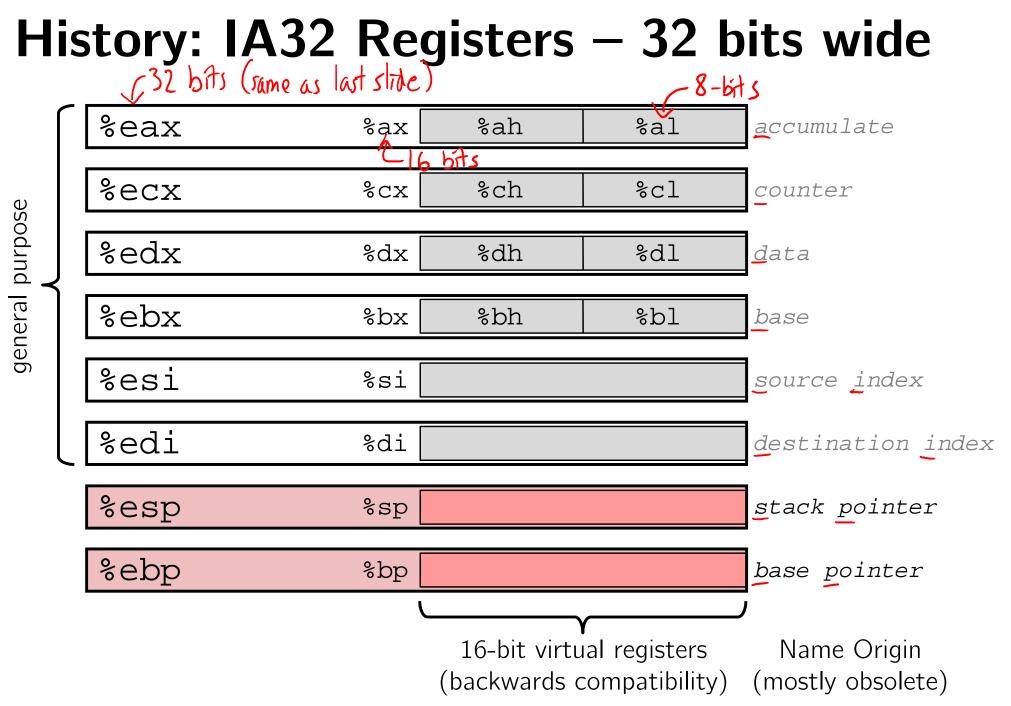

#### x86-64 Integer Registers – 64 bits wide

| 564 bits | J 32 bits | √ 64 bits | C 32 bits |

|----------|-----------|-----------|-----------|

| %rax     | %eax      | %r8       | %r8d      |

| %rbx     | %ebx      | %r9       | %r9d      |

| %rcx     | %ecx      | %r10      | %r10d     |

| %rdx     | %edx      | %r11      | %rlld     |

| %rsi     | %esi      | %r12      | %r12d     |

| %rdi     | %edi      | %r13      | %r13d     |

| %rsp     | %esp      | %r14      | %r14d     |

| %rbp     | %ebp      | %r15      | %r15d     |

Can reference low-order 4 bytes (also low-order 2 & 1 bytes)

| Memory |

|--------|

|--------|

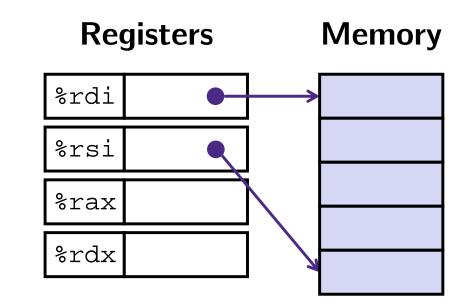

#### Registers VS.

- Addresses

- 0x7FFFD024C3DC

- ✤ Big

- ~ 8 GiB

- Slow VS.

- ~50-100 ns

- Dynamic

- Can "grow" as needed while program runs

Names VS.

#### %rdi

- Small VS.  $(16 \times 8 B) = 128 B$

- Fast

- - sub-nanosecond timescale

#### vs. Static

fixed number in hardware

#### **Three Basic Kinds of Instructions**

- 1) Transfer data between memory and register

- Load data from memory into register

- %reg = Mem[address]

- Store register data into memory

- Mem[address] = %reg

**Remember:** Memory is indexed just like an array of bytes!

- 2) Perform arithmetic operation on register or memory data

- c = a + b; z = x << y; i = h & g;</pre>

- 3) Control flow: what instruction to execute next

- Unconditional jumps to/from procedures

- Conditional branches

stack.

data at that address

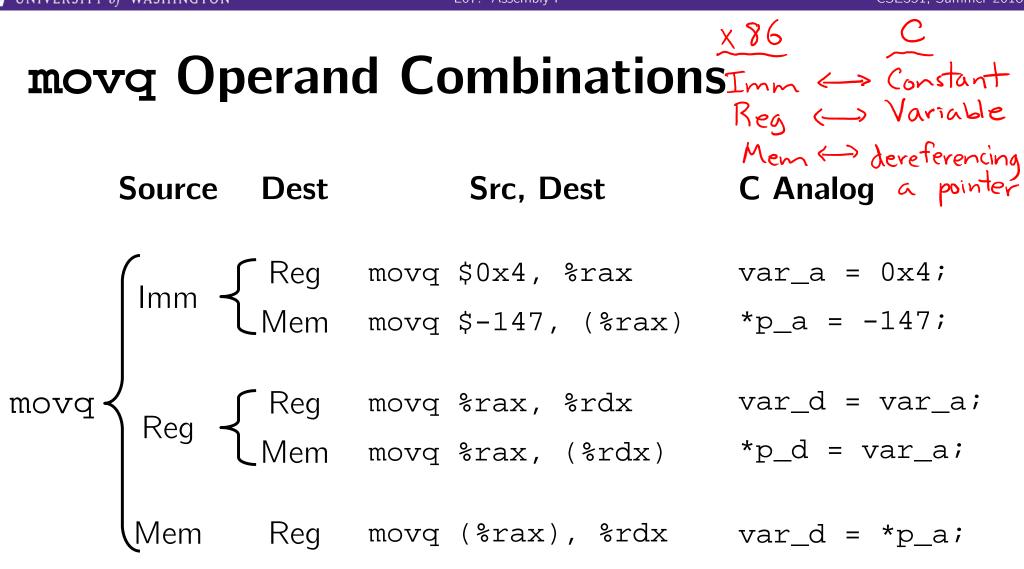

## **Operand types**

- *Immediate:* Constant integer data

- Examples: \$0x400, \$-533 hex decimal Like C literal, but prefixed with '\$'

- Encoded with 1, 2, 4, or 8 bytes depending on the instruction

- **Register:** 1 of 16 integer registers

- Examples: %rax, %r13

- But %rsp reserved for special use

- pointer Others have special uses for particular instructions

- ✤ Memory: Consecutive bytes of memory at a computed address

- take data in % rax, ■ Simplest example: (%rax 🧲 treat as address,

- Various other "address modes"

|            | %rax       |

|------------|------------|

|            | %rcx       |

|            | %rdx       |

|            | %rbx       |

|            | %rsi       |

|            | %rdi       |

| $\uparrow$ | %rsp       |

|            | %rbp       |

| -          |            |

|            | 8rN r8-r15 |

#### **Moving Data**

- \* General form: (mov\_\_\_\_\_\_\_\_\_\_\_\_, destination

- Missing letter (\_) specifies size of operands

- Note that due to backwards-compatible support for 8086 programs (16-bit machines!), "word" means 16 bits = 2 bytes in x86 instruction names

- \* mov<u>b</u> src, dst

- Move 1-byte "byte"

- \* movw\_src, dst

- Move 2-byte "word"

- \* movl src, dst

- Move 4-byte "long word"

- \* movg src, dst

- Move 8-byte "quad word"

Cannot do memory-memory transfer with a single instruction () Men→Reg move (<sup>3</sup>rax), <sup>3</sup>rdx

How would you do it? (2) Reg→Mem move <sup>3</sup>rdx, (<sup>3</sup>rbx)

#### x86-64 Introduction

- Arithmetic operations

- Memory addressing modes

- swap example

- Address computation instruction (lea)

## **Some Arithmetic Operations**

- Binary (two-operand) instructions:

- Maximum of one memory operand

- Beware argument order (AT&T syntax)

- No notion of datatypes

- Just bits!

- Only arithmetic vs. logical shifts

- How do you

implement

"r3 = r1 + r2

| erand    | d) inst                      | ructio                             | ons:                          | _ Imi                   | n, Reg, or                   | Mem                                            |

|----------|------------------------------|------------------------------------|-------------------------------|-------------------------|------------------------------|------------------------------------------------|

| ie       | F                            | ormat                              |                               | Comp                    | utation                      |                                                |

| d        | addq                         | src,                               | dst                           | dst = c                 | b + a<br>lst + src           | (dst += src)                                   |

| )<br>)   | subq                         | src,                               | dst                           | dst = d                 | dst – src                    |                                                |

| /        | imulq                        | src,                               | dst                           | dst = d                 | dst * src                    | signed mult                                    |

|          | sarq                         | src,                               | dst                           | dst = d                 | st >> src                    | <b>A</b> rithmetic                             |

|          | shrq                         | src,                               | dst                           | dst = d                 | st >> src                    | Logical                                        |

|          | shlq                         | src,                               | dst                           | dst = d                 | st << src                    | (same as salq)                                 |

|          | xorq                         | src,                               | dst                           | dst = d                 | dst ^ src                    |                                                |

|          | andq                         | src,                               | dst                           | dst = d                 | lst & src                    |                                                |

|          |                              | src,                               | dst                           | dst = d                 | dst   src                    |                                                |

| operat   |                              |                                    |                               | -                       | $(b, w, l, \alpha$           | (p~q)                                          |

| ×<br>2"? | subq %<br>add q %<br>add q % | rex,%rex<br>,rax,%rex<br>.rbx,%rex | # rcx =<br># rcx=<br>( # rcx= | = U<br>= vax<br>rax+rbx | mixing 8, roo<br>add q 9, rb | r, %rex #rex=rex<br>x, %rex #rex=rex+rbx<br>25 |

#### **Some Arithmetic Operations**

Unary (one-operand) Instructions:

| Format          | Computation   |                    |

|-----------------|---------------|--------------------|

| incq dst        | dst = dst + 1 | increment          |

| <b>decq</b> dst | dst = dst – 1 | decrement          |

| <b>negq</b> dst | dst = -dst    | negate             |

| <b>notq</b> dst | dst = ~dst    | bitwise complement |

See CSPP Section 3.5.5 for more instructions: mulq, cqto, idivq, divq

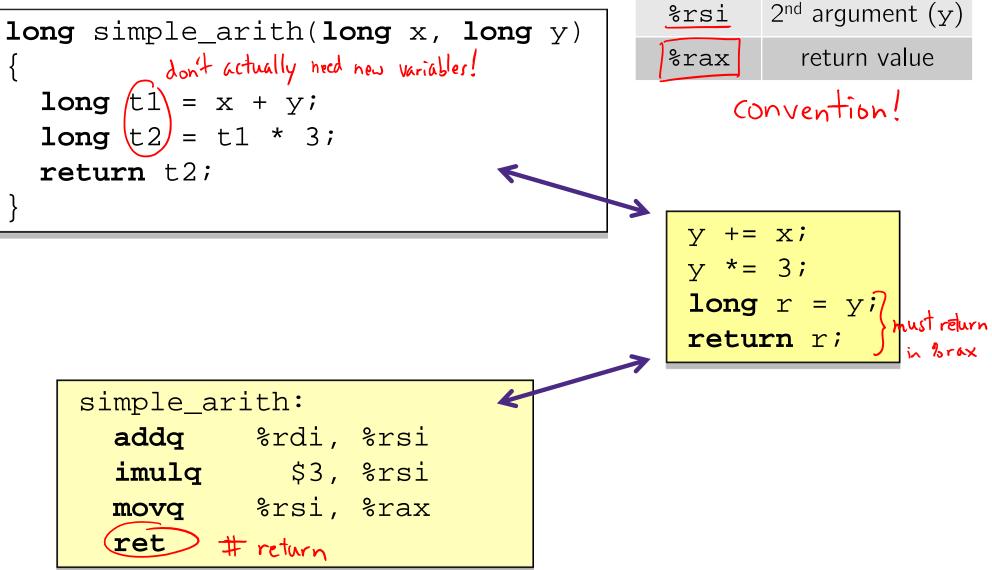

Use(s)

$1^{st}$  argument (x)

Register

%rdi

# Arithmetic Example

11

#### **Example of Basic Addressing Modes**

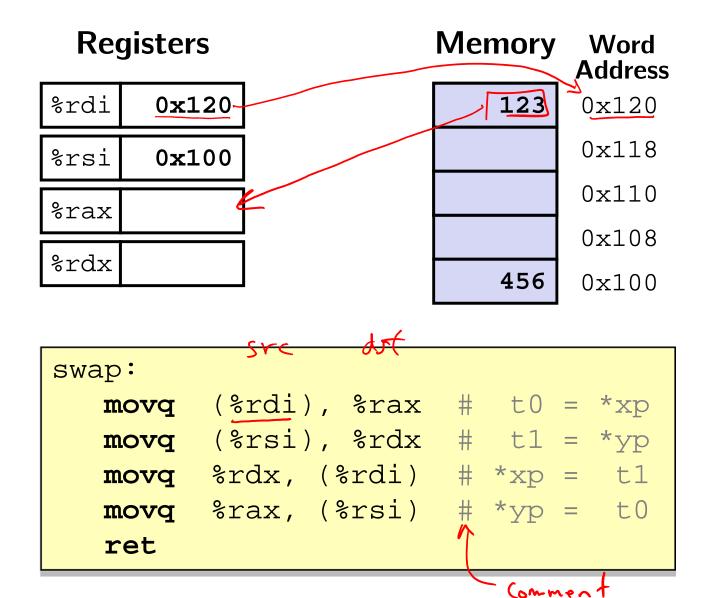

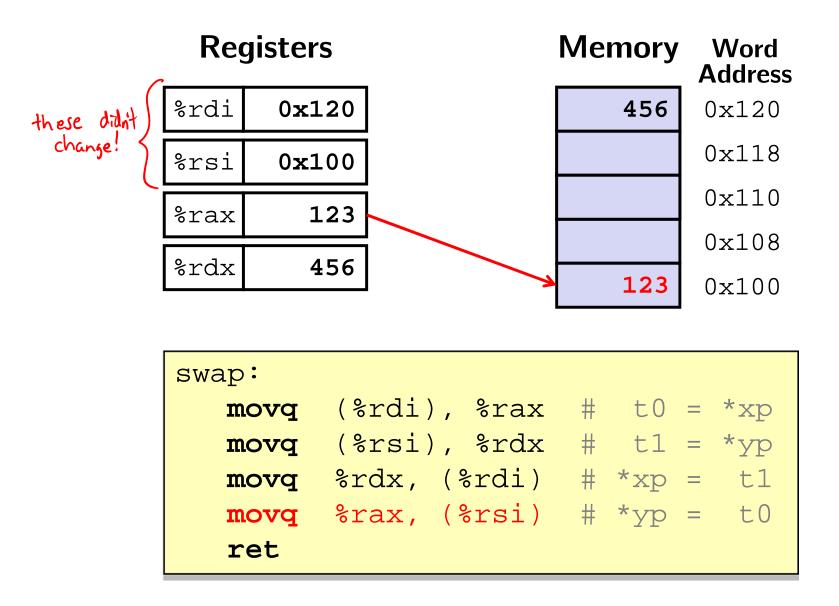

```

void swap(long *xp, long *yp)

{

long t0 = *xp;

long t1 = *yp;

*xp = t1;

*yp = t0;

}

```

| V     |                  |             | 1        | - N    |

|-------|------------------|-------------|----------|--------|

| swap: | Stc              | , dst       | (AT &T : | (mtax) |

| movq  | (%rdi)           | , %rax      |          |        |

| movq  | (%rsi)           |             |          |        |

| movq  |                  | (%rdi)      |          |        |

| movq  | <pre>%rax,</pre> | (%rsi)      |          |        |

| ret   |                  |             |          |        |

|       | Ĭ                | Tem operand | s        |        |

|       |                  | •           |          |        |

```

void swap(long *xp, long *yp)

{

long t0 = *xp;

long t1 = *yp;

*xp = t1;

*yp = t0;

}

```

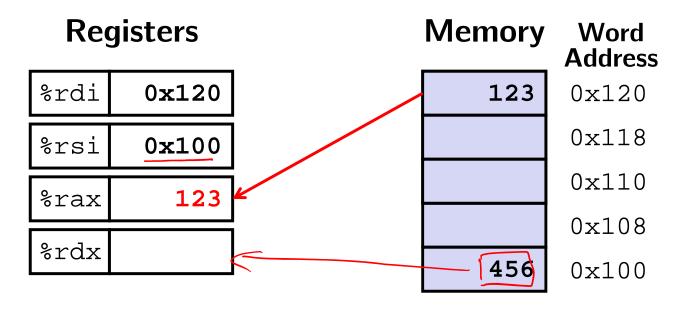

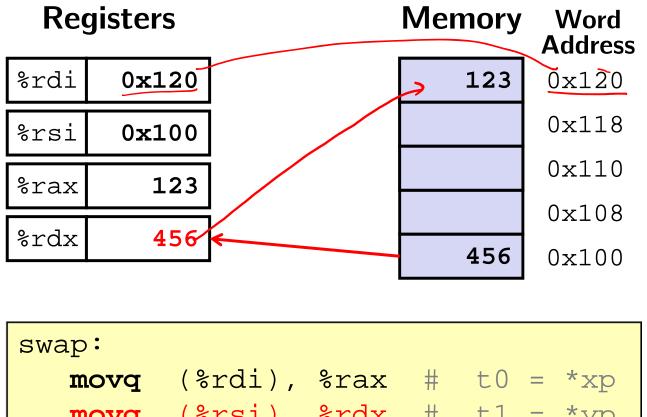

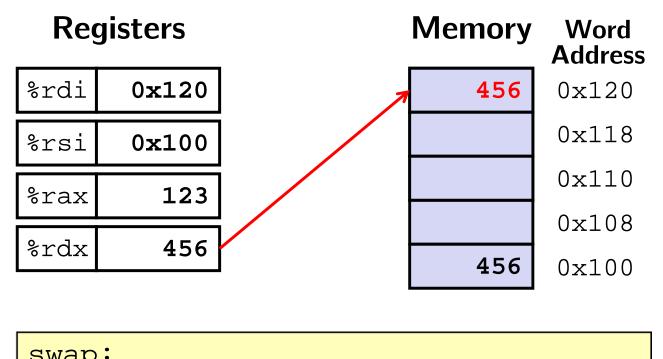

| swap: |              |

|-------|--------------|

| movq  | (%rdi), %rax |

| movq  | (%rsi), %rdx |

| movq  | %rdx, (%rdi) |

| movq  | %rax, (%rsi) |

| ret   |              |

| Registe | <u>ariable</u>    |    |

|---------|-------------------|----|

| %rdi    | $\Leftrightarrow$ | xp |

| %rsi    | $\Leftrightarrow$ | ур |

| %rax    | $\Leftrightarrow$ | t0 |

| %rdx    | $\Leftrightarrow$ | t1 |

| swap: |                         |   |     |   |     |

|-------|-------------------------|---|-----|---|-----|

| movq  | (%rdi), %rax            | # | t0  | = | *xp |

| movq  | (%rsi), %rdx            | # | t1  | = | *yp |

| movq  | <pre>%rdx, (%rdi)</pre> | # | *xp | = | t1  |

| movq  | <pre>%rax, (%rsi)</pre> | # | *yp | = | t0  |

| ret   |                         |   |     |   |     |

| swap. |                       |   |     |   |     |

|-------|-----------------------|---|-----|---|-----|

| movq  | (%rdi), %rax          | # | t0  | = | *xp |

| movq  | (%rsi), %rdx          | # | t1  | = | *yp |

|       | %rdx, ( <u>%rdi</u> ) |   |     |   |     |

| movq  | %rax, (%rsi)          | # | *yp | = | t0  |

| ret   |                       |   |     |   |     |

|       |                       |   |     |   |     |

| swap. |                         |   |     |   |     |

|-------|-------------------------|---|-----|---|-----|

| movq  | (%rdi), %rax            | # | t0  | = | *xp |

| movq  | (%rsi), %rdx            | # | t1  | = | *yp |

| movq  | <pre>%rdx, (%rdi)</pre> | # | *xp | = | t1  |

| movq  | <pre>%rax, (%rsi)</pre> | # | *yp | = | t0  |

| ret   |                         |   |     |   |     |

# Summary

- x86-64 is a complex instruction set computing (CISC) architecture

- Registers are named locations in the CPU for holding and manipulating data

- x86-64 uses 16 64-bit wide registers

- Assembly operands include immediates, registers, and data at specified memory locations