# CSE 311 Foundations of Computing I

Lecture 24 FSM Limits, Connection to Circuits Spring 2013

### Announcements

- Reading assignments

7<sup>th</sup> Edition, Section 13.4

6<sup>th</sup> Edition, Section 12.4

- Homework 7 due today

- Homework 8 out Friday, due Friday, June 7

- Final exam, Monday June 10. Room TBA. Study materials out Friday/Monday.

# Last lecture highlights

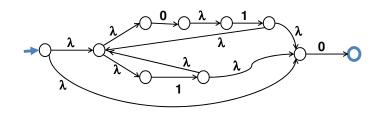

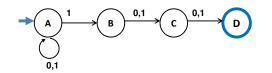

• NFAs from Regular Expressions

**(01 ∪1)\*0**

1

3

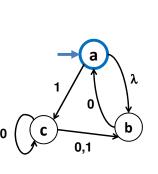

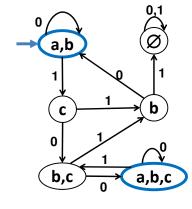

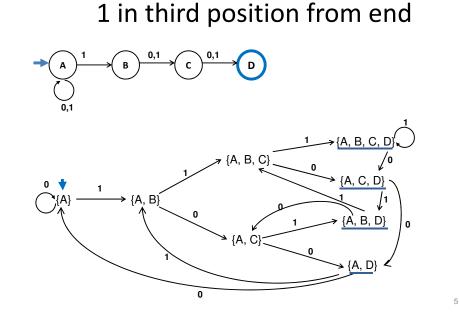

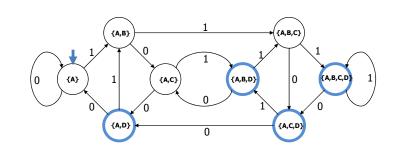

### Last lecture highlights

• "Subset construction": NFA to DFA

2

NFA

DFA

### Redrawing

6

8

# DFAs ≡ Regular Expressions

We have shown how to build an optimal DFA for every regular expression

- Build NFA

- Convert NFA to DFA using subset construction

- Minimize resulting DFA

Theorem: A language is recognized by a DFA iff it has a regular expression

7

# **Generalized NFAs**

- Like NFAs but allow

- Parallel edges

- Regular Expressions as edge labels

- NFAs already have edges labeled  $\lambda$  or a

- An edge labeled by A can be followed by reading a string of input chars that is in the language represented by A

- A string x is accepted iff there is a path from start to final state labeled by a regular expression whose language contains x

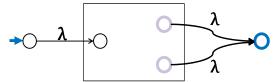

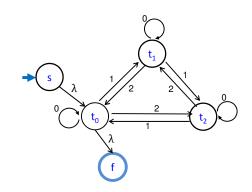

# Starting from NFA

• Add new start state and final state

• Then eliminate original states one by one, keeping the same language, until it looks like:

####

• Final regular expression will be A

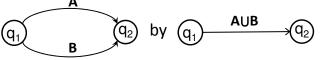

# Only two simplification rules:

• **Rule 1**: For any two states q<sub>1</sub> and q<sub>2</sub> with parallel edges (possibly q<sub>1</sub>=q<sub>2</sub>), replace

Rule 2: Eliminate non-start/final state q<sub>3</sub> by replacing all

$$(q_1)$$

$\xrightarrow{\mathbf{B}}$   $(q_3)$   $\xrightarrow{\mathbf{C}}$   $(q_2)$  by  $(q_1)$   $\xrightarrow{\mathbf{AB*C}}$   $(q_2)$

for *every* pair of states  $q_1$ ,  $q_2$  (even if  $q_1=q_2$ )

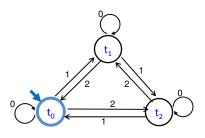

# Converting an NFA to a regular expression

- Consider the DFA for the mod 3 sum

- Accept strings from {0,1,2}\* where the digits mod

3 sum of the digits is 0

# Splicing out a node

- Label edges with regular expressions

- $\begin{array}{rrrr} t_0 {\rightarrow} t_1 {\rightarrow} t_0 : & 10^*2 \\ t_0 {\rightarrow} t_1 {\rightarrow} t_2 : & 10^*1 \\ t_2 {\rightarrow} t_1 {\rightarrow} t_0 : & 20^*2 \\ t_2 {\rightarrow} t_1 {\rightarrow} t_2 : & 20^*1 \end{array}$

9

11

12

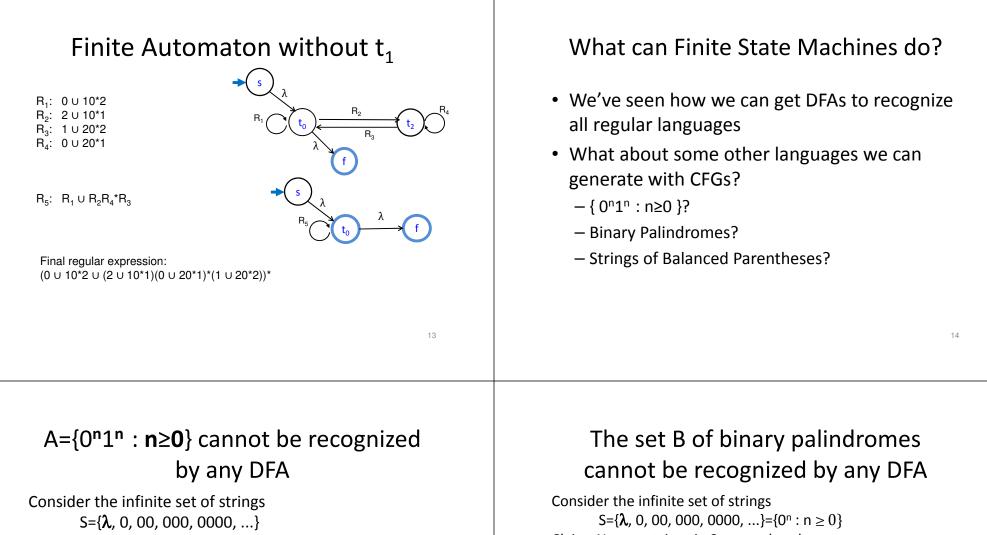

Claim: No two strings in S can end at the same state of any DFA for A

Proof: Suppose  $n \neq m$  and  $0^n$  and  $0^m$  end at the same state p.

Since O<sup>n</sup>1<sup>n</sup> is in A, following 1<sup>n</sup> after state p must lead to a final state.

But then the DFA would accept 0<sup>m</sup>1<sup>n</sup>

which is a contradiction to the DFA recognizing A.  $\Box$ Given claim, the # of states of any DFA for A must be  $\geq |S|$ which is not finite, which is impossible for a DFA. Consider the infinite set of strings S={λ, 0, 00, 000, 0000, ...}={0<sup>n</sup> : n ≥ 0}

Claim: No two strings in S can end at the same state of any DFA for B

Proof: Suppose n≠m and 0<sup>n</sup> and 0<sup>m</sup> end at the same state p. Since 0<sup>n</sup>10<sup>n</sup> is in B, following 10<sup>n</sup> after state p must lead to a final state.

But then the DFA would accept 0<sup>m</sup>10<sup>n</sup> which is not in B and is a contradiction since the DFA recognizes B. □

Given claim, the # of states of any DFA for A must be  $\geq$  |S| which is not finite, which is impossible for a DFA.

15

- The set P of strings of balanced parentheses cannot be recognized by any DFA

- What infinite set of simple strings can we choose that all must go to different states?

- For each pair of strings in this set what common extension should we choose that shows that they can't go to the same state?

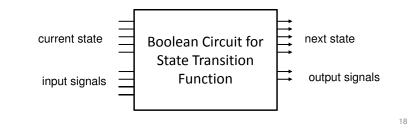

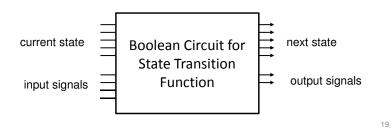

### FSMs in Hardware

- Encode the states in binary: e.g. states 0,1,2,3 represented as 000,100, 010,001, or as 00,01,10,11.

- Encode the input symbols as binary signals

- Encode the outputs possible as binary signals

- Build combinational logic circuit to compute transition function:

### FSMs in Hardware

17

- Combine with sequential logic for

- Registers to store bits of state

- Clock pulse

- At start of clock pulse, current state bits from registers and input signals are released to the circuit

- At end of clock pulse, output bits are produced and next state bits are stored back in the same registers

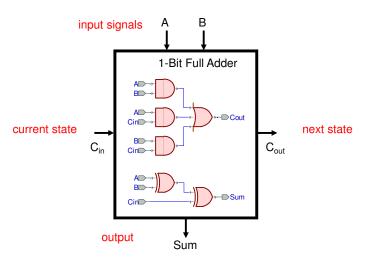

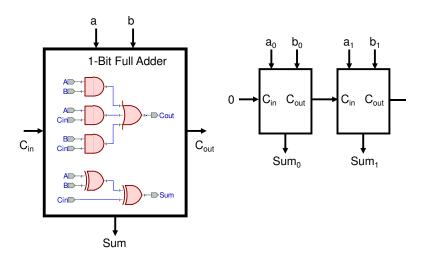

# Example: 1-bit Full Adder

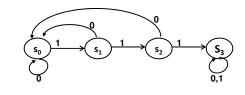

# FSM for binary addition

Assume that the two integers are a<sub>n-1</sub>...a<sub>2</sub>a<sub>1</sub>a<sub>0</sub> and b<sub>n-1</sub>...b<sub>2</sub>b<sub>1</sub>b<sub>0</sub> and bits arrive together as [a<sub>0</sub>,b<sub>0</sub>] then [a<sub>1</sub>,b<sub>1</sub>] etc.

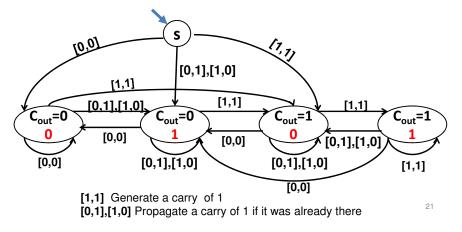

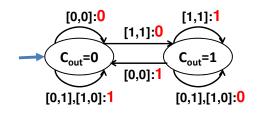

# FSM for binary addition using output on edges

Assume that the two integers are a<sub>n-1</sub>...a<sub>2</sub>a<sub>1</sub>a<sub>0</sub> and b<sub>n-1</sub>...b<sub>2</sub>b<sub>1</sub>b<sub>0</sub> and bits arrive together as [a<sub>0</sub>,b<sub>0</sub>] then [a<sub>1</sub>,b<sub>1</sub>] etc.

[1,1] Generate a carry of 1[0,1],[1,0] Propagate a carry of 1 if it was already there

# FSMs without sequential logic

- What if the entire input bit-strings are available at all once at the start?

- E.g. 64-bit binary addition

- Don't want to wait for 64 clock cycles to compute the output!

- Suppose all input strings have length **n**

- Can chain together n copies of the state transition circuit as one big combinational logic circuit

# A 2-bit ripple-carry adder

23

### Problem with Chaining Transition Circuits

- Resulting Boolean circuit is "deep"

- There is a small delay at each gate in a Boolean circuit

- The clock pulse has to be long enough so that all combinational logic circuits can be evaluated during a single pulse

- Deep circuits mean slow clock.

### Carry-Look-Ahead Adder

Compute generate  $G_i = a_i \wedge b_i$  [1,1] propagate  $P_i = a_i \bigoplus b_i$  [0,1],[1,0] These determine transition and output functions - Carry  $C_i = G_i \vee (P_i \wedge C_{i-1})$  also written  $C_i = G_i + P_i C_{i-1}$ - Sum<sub>i</sub> =  $P_i \bigoplus C_{i-1}$ Unwinding, we get  $C_0 = G_0 \quad C_1 = G_1 + G_0 P_1 \quad C_2 = G_2 + G_1 P_2 + G_0 P_1 P_2$   $C_3 = G_3 + G_2 P_3 + G_1 P_2 P_3 + G_0 P_1 P_2 P_3 P_4$ etc.

### Carry-Look-Ahead Adder

Compute all generate  $G_i = a_i \wedge b_i$  [1,1] propagate  $P_i = a_i \bigoplus b_i$  [0,1],[1,0]

Then compute all:

$\begin{array}{cccc} C_0 = G_0 & C_1 = G_1 + G_0 P_1 & C_2 = G_2 + G_1 P_2 + G_0 P_1 P_2 \\ C_3 = G_3 + G_2 P_3 + G_1 P_2 P_3 + G_0 P_1 P_2 P_3 \\ C_4 = G_4 + G_3 P_4 + G_2 P_3 P_4 + G_1 P_2 P_3 P_4 + G_0 P_1 P_2 P_3 P_4 & \text{etc.} \end{array}$  Finally, use these to compute

$$\begin{split} & \text{Sum}_0 = \text{P}_0 \quad \text{Sum}_1 = \text{P}_1 \bigoplus \text{C}_0 \quad \text{Sum}_2 = \text{P}_2 \bigoplus \text{C}_1 \\ & \text{Sum}_3 = \text{P}_3 \bigoplus \text{C}_2 \quad \text{Sum}_4 = \text{P}_4 \bigoplus \text{C}_3 \quad \text{Sum}_5 = \text{P}_5 \bigoplus \text{C}_4 \text{ etc} \end{split}$$

If all C<sub>1</sub> are computed using 2-level logic, total depth is 6.

### Smaller Fast Adders?

Carry-look-ahead circuit for carry  $C_{n-1}$ has 2 + 3 +...+ n = (n+2)(n-1)/2 gates – a lot more than ripple-carry adder circuit.

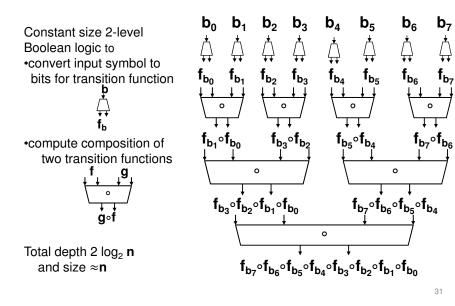

Can do this with roughly 2  $\log_2 n$  depth and linear size using ideas from DFAs

27

# Speed things up but stay small?

- To go faster, work on both 1<sup>st</sup> half and 2<sup>nd</sup> half of the input at once

- How can you determine action of FSM on 2<sup>nd</sup> half without knowing state reached after reading 1<sup>st</sup> half?

$b_1b_2...b_{n/2}b_{n/2+1}...b_{n-1}b_n$ what state?

• Idea: Figure out what happens in 2<sup>nd</sup> half for all possible values of the middle state at once

29

**b**<sub>7</sub>

31

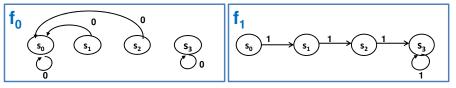

### Transition Function Composition

Transition table gives a function for each input symbol

State reached on input **b**<sub>1</sub>...**b**<sub>n</sub> is  $f_{b_n}(f_{b_{n-1}}...(f_{b_2}(f_{b_1}(start)))...) = f_{b_n} \circ f_{b_{n-1}}... \circ f_{b_2} \circ f_{b_1}(start)$

### **Transition Function Composition**

# Computing all the values

We need to compute all of  $\mathbf{f}_{b_7} \circ \mathbf{f}_{b_6} \circ \mathbf{f}_{b_5} \circ \mathbf{f}_{b_4} \circ \mathbf{f}_{b_3} \circ \mathbf{f}_{b_1} \circ \mathbf{f}_{b_1} \circ \mathbf{f}_{b_0}$  Already computed  $\mathbf{f}_{\mathbf{b}_6} \circ \mathbf{f}_{\mathbf{b}_5} \circ \mathbf{f}_{\mathbf{b}_4} \circ \mathbf{f}_{\mathbf{b}_3} \circ \mathbf{f}_{\mathbf{b}_2} \circ \mathbf{f}_{\mathbf{b}_1} \circ \mathbf{f}_{\mathbf{b}_0} = \mathbf{f}_{\mathbf{b}_6} \circ (\mathbf{f}_{\mathbf{b}_5} \circ \mathbf{f}_{\mathbf{b}_4}) \circ (\mathbf{f}_{\mathbf{b}_3} \circ \mathbf{f}_{\mathbf{b}_2} \circ \mathbf{f}_{\mathbf{b}_1} \circ \mathbf{f}_{\mathbf{b}_n})$  $f_{b_{5}} \circ f_{b_{4}} \circ f_{b_{3}} \circ f_{b_{2}} \circ f_{b_{1}} \circ f_{b_{0}} = (f_{b_{5}} \circ f_{b_{4}}) \circ (f_{b_{3}} \circ f_{b_{2}} \circ f_{b_{1}} \circ f_{b_{0}})$  $= \mathbf{f}_{b_4} \circ (\mathbf{f}_{b_3} \circ \mathbf{f}_{b_2} \circ \mathbf{f}_{b_1} \circ \mathbf{f}_{b_0})$  $f_{b_4} \circ f_{b_3} \circ f_{b_2} \circ f_{b_1} \circ f_{b_0}$  $\mathbf{f}_{b_3} \circ \mathbf{f}_{b_2} \circ \mathbf{f}_{b_1} \circ \mathbf{f}_{b_0}$ Already computed f<sub>b2</sub>of<sub>b1</sub>of<sub>b0</sub>  $= \mathbf{f}_{b_2} \circ (\mathbf{f}_{b_1} \circ \mathbf{f}_{b_0})$ f<sub>b1</sub>∘f<sub>b0</sub> Already computed f<sub>bo</sub> Already computed

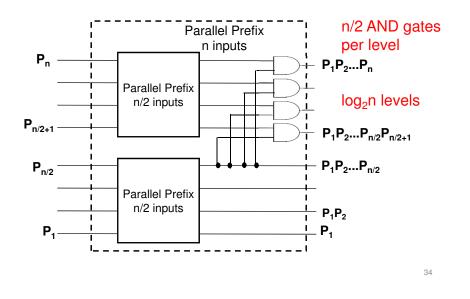

# Parallel Prefix Circuit

- The general way of doing this efficiently is called a parallel prefix circuit

- Designed and analyzed by Michael Fischer and Richard Ladner (University of Washington)

- Uses an adder composition operation that sets

G"= G'+G P' and P"= P'P

- we just show it for the part for computing P" which is a Parallel Prefix AND Circuit

# The Parallel Prefix AND Circuit

### Parallel Prefix Adder

- Circuit depth 2 log<sub>2</sub> n Circuit size 4 n log<sub>2</sub> n

- Can get linear size if depth goes to 2 log<sub>2</sub>n+2

- Actual adder circuits in hardware use combinations of these ideas and more but this gives the basics

- Nice overview of adder circuits at http://www.aoki.ecei.tohoku.ac.jp/arith/mg/algorithm.html