|                                            | <u>Cray (Tera) MTA</u>                                                         |                     |

|--------------------------------------------|--------------------------------------------------------------------------------|---------------------|

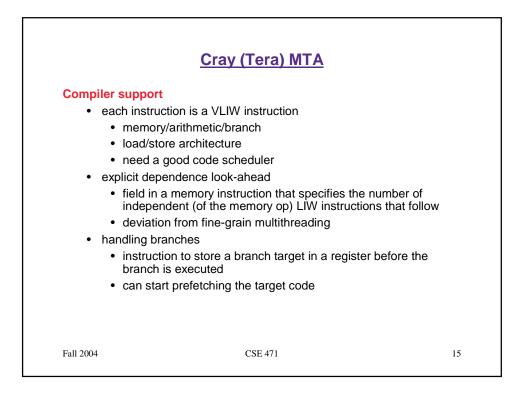

| Fine-grain multith                         | eaded processor                                                                |                     |

| <ul> <li>can switch to</li> </ul>          | a different thread each cycle                                                  |                     |

| <ul> <li>switches</li> </ul>               | to ready threads only                                                          |                     |

|                                            | xecution to remain with the current the of cycles (discussed under compiler    |                     |

| <ul> <li>up to 128 ha</li> </ul>           | rdware contexts                                                                |                     |

| <ul> <li>lots of la<br/>network</li> </ul> | tency to hide, mostly from the multi-h                                         | nop interconnectior |

|                                            | instruction latency is 70-cycles (at or<br>nstruction streams needed to hide a |                     |

| <ul> <li>processor st</li> </ul>           | ate for all 128 contexts                                                       |                     |

| <ul> <li>GPRs (tell</li> </ul>             | otal of 4K registers!)                                                         |                     |

| <ul> <li>status re</li> </ul>              | gisters (includes the PC)                                                      |                     |

| <ul> <li>branch t</li> </ul>               | arget registers                                                                |                     |

|                                            |                                                                                |                     |

| Fall 2004                                  | CSE 471                                                                        | 10                  |

|           | <u>Cray (Tera) MTA</u>                                                                                                                                                                                                                                                                                                                                                                                          |    |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| • (       | <ul> <li>cing features</li> <li>Driginally no data caches</li> <li>to avoid having to keep caches coherent (topic of the next lecture section)</li> <li>increases the latency for data accesses but reduces the variation</li> <li>1 &amp; L2 instruction caches</li> <li>instruction accesses are more predictable &amp; have no coherent problem</li> <li>prefetch straight-line &amp; target code</li> </ul> | су |

| Fall 2004 | CSE 471                                                                                                                                                                                                                                                                                                                                                                                                         | 11 |

| <u>Cray (Tera) MTA</u>                                                                                                                                                                                                                                    |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| <ul> <li>Interesting features</li> <li>Trade-off between avoiding memory bank conflicts &amp; exploiting spatial locality</li> <li>memory distributed among hardware contexts (processors)</li> </ul>                                                     |  |  |

| <ul> <li>memory addresses are randomized to avoid conflicts</li> <li>want to fully utilize all memory bandwidth</li> <li>run-time system can confine consecutive virtual addresses to a single (close-by) memory unit</li> <li>reduces latency</li> </ul> |  |  |

| used mainly for instructions                                                                                                                                                                                                                              |  |  |

| Fall 2004 CSE 471 12                                                                                                                                                                                                                                      |  |  |

|            | <u>Cray (Tera) MTA</u>                                                                                                 |          |

|------------|------------------------------------------------------------------------------------------------------------------------|----------|

| Interestin | ng features                                                                                                            |          |

| • ta       | gged memory for synchronization                                                                                        |          |

|            | <ul> <li>indirectly set full/empty bits to prevent data races</li> </ul>                                               |          |

|            | <ul> <li>prevents a consumer/producer from loading/over<br/>value before a producer/consumer has written/re</li> </ul> |          |

|            | <ul> <li>set to empty when producer instruction starts</li> </ul>                                                      | S        |

|            | <ul> <li>consumer instructions block if try to read the<br/>value</li> </ul>                                           | producer |

|            | <ul> <li>set to full when producer value is written</li> </ul>                                                         |          |

|            | <ul> <li>consumers can now read a valid value</li> </ul>                                                               |          |

|            | <ul> <li>explicitly set full/empty bits for synchronization</li> </ul>                                                 |          |

|            | <ul> <li>primarily used to synchronize threads that are ac<br/>shared data (topic of the next lecture)</li> </ul>      | cessing  |

|            | <ul> <li>lock: read memory location &amp; set to empty</li> </ul>                                                      |          |

|            | <ul> <li>other readers are blocked</li> </ul>                                                                          |          |

|            | <ul> <li>unlock: write &amp; set to full</li> </ul>                                                                    |          |

| Fall 2004  | CSE 471                                                                                                                | 13       |

Г

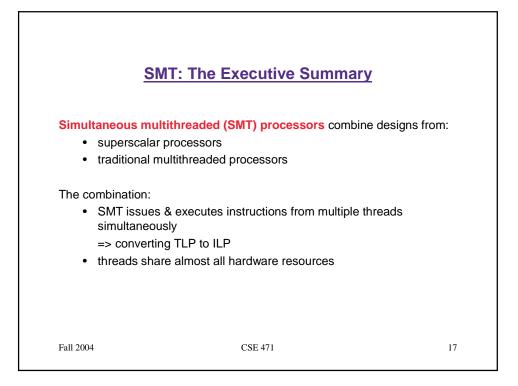

|                       | An SMT Architecture                                                                                               |         |  |

|-----------------------|-------------------------------------------------------------------------------------------------------------------|---------|--|

| Three primary goals   | s for this architecture:                                                                                          |         |  |

| 1. Achieve sign       | ificant throughput gains with multiple                                                                            | threads |  |

| 2. Minimize the alone | <ol><li>Minimize the performance impact on a single thread executing<br/>alone</li></ol>                          |         |  |

|                       | <ol> <li>Minimize the microarchitectural impact on a conventional out-of-<br/>order superscalar design</li> </ol> |         |  |

|                       |                                                                                                                   |         |  |

|                       |                                                                                                                   |         |  |

|                       |                                                                                                                   |         |  |

|                       |                                                                                                                   |         |  |

|                       |                                                                                                                   |         |  |

| Fall 2004             | CSE 471                                                                                                           | 20      |  |

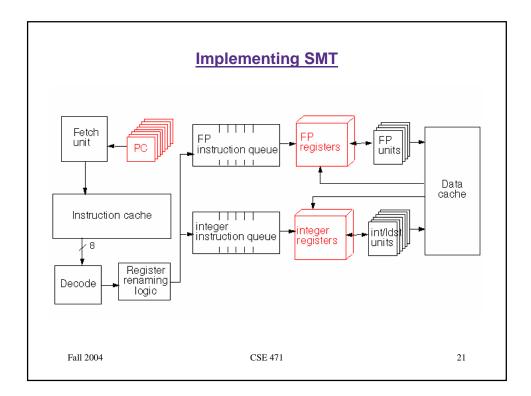

| Per-thread hard                                                                                  | ware                                                                                                |                  |

|--------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------------------|

| <ul> <li>small stuff</li> </ul>                                                                  | f                                                                                                   |                  |

| <ul> <li>all part of</li> </ul>                                                                  | current out-of-order processors                                                                     |                  |

| <ul> <li>none enda</li> </ul>                                                                    | angers the cycle time                                                                               |                  |

| <ul> <li>progra</li> <li>return</li> <li>thread</li> <li>per-thread</li> <li>instruct</li> </ul> | l identifiers, e.g., with BTB entries<br>I bookkeeping for<br>ction queue flush<br>ction retirement | , TLB entries    |

| This is why there                                                                                | is only a 10% increase to Alpha 2                                                                   | 21464 chip area. |

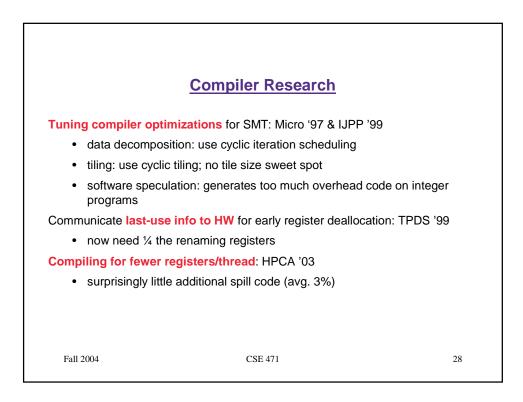

|                                       | Architecture Research                            |                     |  |

|---------------------------------------|--------------------------------------------------|---------------------|--|

| Concept & potentia<br>Anniversary Ant | al of Simultaneous Multithreading: Is<br>thology | SCA '95 & ISCA 25th |  |

| Designing the micr                    | oarchitecture: ISCA '96                          |                     |  |

| <ul> <li>straightforw</li> </ul>      | ard extension of out-of-order supers             | scalars             |  |

| I-fetch thread choo                   | I-fetch thread chooser: ISCA '96                 |                     |  |

| <ul> <li>40% faster t</li> </ul>      | than round-robin                                 |                     |  |

| The <b>lockbox</b> for ch             | neap synchronization: HPCA '98                   |                     |  |

| <ul> <li>orders of ma</li> </ul>      | agnitude faster                                  |                     |  |

| can parallel                          | ize previously unparallelizable code             | S                   |  |

|                                       |                                                  |                     |  |

|                                       |                                                  |                     |  |

| Fall 2004                             | CSE 471                                          | 26                  |  |

| SMT Collaborators                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                              |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| UW<br>Hank Levy<br>Steve Gribble<br>Dean Tullsen (UCSD)<br>Jack Lo (VMWare)<br>Sujay Parekh (IBM Yorktown)<br>Brian Dewey (Microsoft)<br>Manu Thambi (Microsoft)<br>Josh Redstone (Google)<br>Mike Swift<br>Luke McDowell (Naval<br>Academy)<br>Steve Swanson<br>Aaron Eakin (HP)<br>Dimitriy Portnov (Google) | DEC/Compaq<br>Joel Emer (now Intel)<br>Rebecca Stamm<br>Luiz Barroso (now Google)<br>Kourosh Gharachorloo (now Google)<br>For more info on SMT:<br>http://www.cs.washington.edu/research/smt |  |  |

| Fall 2004 CS                                                                                                                                                                                                                                                                                                   | SE 471 31                                                                                                                                                                                    |  |  |