## Conceptual execution on a processor which exploits ILP

- · Instruction fetch and branch prediction

- Corresponds to IF in simple pipeline

- Complicated by multiple issue and the potential need to fetch more than one basic block at a time (see later)

- · Instruction decode, dependence check, dispatch, issue

- Corresponds (many variations) to ID

- Although instructions are issued (i.e., assigned to functional units), they

might not execute right away (cf. reservation stations)

- · Instruction execution

- Corresponds to EX and/or MEM (with various latencies)

- · Instruction commit

- Corresponds to WB (see later) but more complex because of speculation and out-of-order completion

10/26/01

Reg. Renaming CSE 471 Autumn 01

### Register renaming - Generalities

- Use a physical register file (or other storage form, e.g., reservation station or reorder buffer) larger than the ISA logical one

- · When instruction is decoded

- Give a new name to result register from free list. The register is

- Give source operands their physical names (from mapping table)

10/26/01

Reg. Renaming CSE 471 Autumn 01

#### Register renaming -- Requirements

- · Keep a mapping table logical physical correspondence

- Because of branch prediction, need to save the mapping table when predicting branch

- · Keep a free list of empty physical registers

- Note that several physical registers can be mapped to the same logical register (corresponding to instructions at different times; avoids WAW hazards)

10/26/0

Reg. Renaming CSE 471 Autumn 01

# Register renaming – Scheme 1: File of physical registers

- · Extra set of registers

- · At decode:

- Rename the result register (get from free list; update mapping table). If none available, we have a structural hazard

- When a physical register has been read for the last time, return it to the free list

- Have a counter associated with each physical register (+ when a source logical register is renamed to physical register; - when instruction uses physical register as operand; release when counter is 0)

- Simpler to wait till logical register has been assigned a new name by a later instruction and that later instruction has been committed

10/26/01

Reg. Renaming CSE 471 Autumn 01

#### Scheme 1: Example

Before: add r3,r3,4 after add r37,r3,4 add r4,r7,r3 add r38,r7,r37 add r39,r2,r7

Free list r37,r38,r39 .... r2, r3, r4, r7 not renamed yet

At this point r3 is remapped from r37 to r39 When r39 commits, r37 will be returned to the

free list

10/26/01 Reg. Renaming CSE 471 Autumn 01

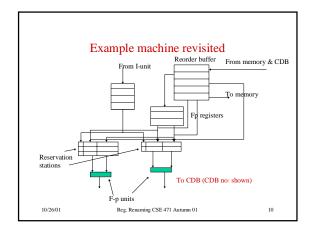

### Register renaming – Scheme 2; Reorder buffer

- Use of a reorder buffer

- Reorder buffer = circular queue with head and tail pointers

- At issue (renaming time), an instruction is assigned an entry at the tail of the reorder buffer which becomes the name of (or a pointer to) the result register

- At end of functional-unit computation, value is put in the instruction reorder buffer's position

- When the instruction reaches the head of the buffer, its value is stored in the logical or physical (other reorder buffer entry) register.

- Still need of a mapping table

10/26/01

Reg. Renaming CSE 471 Autumn 01

#### Scheme 2: Example

Before: add r3,r3,4 after add rob6,r3,4 add r4,r7,r3 add rob7,r7,rob6 add r3, r2, r7 add rob8,r2,r7

Assume reorder buffer is initially at position 6 and has more than 8 slots

10/26/01

Reg. Renaming CSE 471 Autumn 01

#### Data dependencies with register renaming

- Register renaming does not get rid of RAW dependencies

- Still need for forwarding or for indicating whether a register has received its value

- Register renaming gets rid of WAW and WAR dependencies

- The reorder buffer, as its name implies, can be used for inorder completion

10/26/01 Reg. Renaming CSE 471 Autumn 01

#### More on reorder buffer

- Tomasulo's scheme can be extended with the possibility of completing instructions in order

- Reorder buffer entry contains (this is not the only possible solution)

- Type of instruction (branch, store, ALU, or load)

- Destination (none, memory address, register)

- Value and its presence/absence

- · Replaces load/store buffers

- Reservation station tags and "true" register tags are now ids of entries in the reorder buffer

10/26/01

Reg. Renaming CSE 471 Autumn 01

#### Need for 4 stages

- · In Tomasulo's solution 3 stages: issue, execute, write

- Now 4 stages: issue, execute, write, commit

- · Dispatch and Issue

- Check for structural hazards (reservation stations busy, reorder buffer full). If one exists, stall the instruction and those following

- If dispatch possible, send values to reservation station if the values are available in either the registers or the reorder buffer. Otherwise send tag

- Allocate an entry in the reorder buffer and send its number to the reservation station

- When both operands are ready, issue to functional unit

10/26/01

Reg. Renaming CSE 471 Autumn 01

11

#### Need for 4 stages (c'ed)

- Execute

- Write

- Broadcast on common data bus the value and the tag (reorder buffer number). Reservation stations, if any match the tag, and reorder buffer (always) grab the value.

- Commit

- When instr. at head of the reorder buffer has its result in the buffer it stores it in the real register (for ALU) or memory (for store). The reorder buffer entry (and/or physical register) is freed.

12

10/26/01 Reg. Renaming CSE 471 Autumn 01

| Entry #      | Instruc   | tion     |          | Reorder       | buffer<br>Execu | ite     | Write 1 | result | Commit  |

|--------------|-----------|----------|----------|---------------|-----------------|---------|---------|--------|---------|

| 1            | Load F    | 6, 34(r2 | 2) y     | es            | yes             |         | ye      | s      | yes     |

| 2            | Load F    | 2, 45(r3 | 3) y     | es            | yes             |         |         |        |         |

| 3            | Mul F0,   | F2, F4   | y        | es            |                 |         |         |        |         |

| 4            | Sub F8,   | F6, F2   | ye       | es            |                 |         |         |        |         |

| 5            | Div F10   | , F0, F6 | ye.      | es            |                 |         |         |        |         |

| 6            | Add F6,l  | F8,F2    | ye<br>Re | s<br>servatio | n Stations      | :       |         |        | Y 100 4 |

| Name         | Busy      | Fm       | Vj       | Vk            | Qj              | Qk      |         |        | Initial |

| Add 1        | yes       | Sub      | (#1)     |               |                 | (#2)    |         |        |         |

| Add2<br>Add3 | yes<br>no | Add      |          |               | (#4)            | (#2)    |         |        |         |

| Mul1         | yes       | Mul      |          | (F4)          | (#2)            |         |         |        |         |

| Mul2         | yes       | Div      |          | (#1)          | (#3)            |         |         |        |         |

|              |           |          | Re       | gister st     | tatus           |         |         |        |         |

| F0 (#3)      | F2 (#2    | ?) F4    | () F6    | 5(#6)         | F8 (#4)         | F10     | (#5) I  | F12    |         |

| 10/26/01     |           |          | Reg.     | Renamin       | g CSE 471 A     | utumn 0 | 1       |        | 13      |

| Entry #      | Instru          | ction     |          | Reorder         | buffer<br>Execu | ıte      | Write result | Commit         |

|--------------|-----------------|-----------|----------|-----------------|-----------------|----------|--------------|----------------|

| 1            | Load I          | 76, 34(r2 | 2) y     | es              | yes             | 3        | yes          | yes            |

| 2            | Load F2, 45(r3) |           | 3) y     | es              | yes             |          | yes          | yes            |

| 3            | Mul FO          | , F2, F4  | . y      | es              | yes             |          |              |                |

| 4            | Sub F8          | , F6, F2  | y        | es              | ye.             | s        | Cycle        | after 2nd load |

| 5            | Div F10         | ), F0, F6 | 5 ye     | es              |                 |          | has co       | ommitted       |

| 6            | Add F6          | ,F8,F2    | ye<br>Re | es<br>servation | Station         | s        |              |                |

| Name         | Busy            | Fm        | Vj       | Vk              | Qj              | Qk       |              |                |

| Add 1        | no              |           |          |                 |                 |          |              |                |

| Add2<br>Add3 | yes<br>no       | Add       |          | (#2)            | (#4)            |          |              |                |

| Mul1         | yes             | Mul       | (#2)     | (F4)            |                 |          |              |                |

| Mul2         | yes             | Div       |          | (#1)            | (#3)            |          |              |                |

|              |                 |           | Re       | gister sta      | itus            |          |              |                |

| F0 (#3)      | F2()            | F4 (      | ) F6(#   | 6) F8           | 3 (#4)          | F10 (#5  | ) F12        |                |

| 10/26/01     |                 |           | Reg.     | Renaming        | CSE 471 A       | autumn 0 | ı            | 14             |

|              |                 |          |              | Reorder                    |         |          | ***         |                                      |

|--------------|-----------------|----------|--------------|----------------------------|---------|----------|-------------|--------------------------------------|

| Entry #      | Instruction     |          | Is           | sue                        | Execute |          | Write resul | t Commit                             |

| 1            | Load F6, 34(r2) |          | , 34(r2) yes |                            | yes     |          | yes         | yes                                  |

| 2            | Load F2, 45(r3) |          | 3) y         | es                         | yes     |          | yes         | yes                                  |

| 3            | Mul F0          | , F2, F4 | у            | es                         | ye      | S        |             |                                      |

| 4            | Sub F8          | F6, F2   | у            | es                         | ye      | s        | yes         |                                      |

| 5            | Div F10, F0, F6 |          |              | es                         |         |          |             | Cycle after sub                      |

| 6            | Add F6,F8,F2    |          | Re           | yes<br>Reservation Station |         | es<br>s  |             | has written its<br>result in reorder |

| Name         | Busy            | Fm       | Vj           | Vk                         | Qj      | Qk       |             | buffer but can't<br>commit yet       |

| Add 1        | no              |          |              |                            |         |          |             | commit yet                           |

| Add2<br>Add3 | yes<br>no       | Add      | (#2)         | (#4)                       |         |          |             |                                      |

| Mul1         | yes             | Mul      | (#2)         | (F4)                       |         |          |             |                                      |

| Mul2         | yes             | Div      |              | (#1)                       | (#3)    |          | Still waiti | ng for #3 to commit                  |

|              |                 |          | Re           | egister st                 | atus    |          |             |                                      |

| F0 (#3)      | F2()            | F4 (     | ) F6(#       | #6) F                      | 8 (#4)  | F10 (#   | 5) F12      |                                      |

| 10/26/01     |                 |          | Reg          | Renaming                   | CSE 471 | Autumn ( | 1           | 15                                   |

| Entry #      | Instru          | ction     | Is     | Reorder<br>sue   | Execut          | e      | Write result    | Commit                  |

|--------------|-----------------|-----------|--------|------------------|-----------------|--------|-----------------|-------------------------|

| 1            | Load l          | F6, 34(r  | 2) y   | es/es            | yes             |        | yes             | yes                     |

| 2            | Load F2, 45(r3) |           |        | es es            | yes             |        | yes             | yes                     |

| 3            | Mul F           | ), F2, F4 | l y    | es es            | yes             |        |                 |                         |

| 4            | Sub F8          | , F6, F2  | . у    | es               | yes             |        | yes             |                         |

| 5            | Div F10         | ), F0, F6 | 5 у    | es               |                 |        |                 |                         |

| 6            | Add F6          | ,F8,F2    | R      | es<br>eservation | yes<br>Stations |        | yes             |                         |

| Name         | Busy            | Fm        | Vj     | Vk               | Qj              | Qk     |                 | after add<br>ritten its |

| Add 1        | no              |           |        |                  |                 |        |                 | in reorder              |

| Add2<br>Add3 | no<br>no        |           |        |                  |                 |        | buffer<br>canno | but<br>t commit         |

| Mul1         | yes             | Mul       | (#2)   | (F4)             |                 |        |                 |                         |

| Mul2         | yes             | Div       |        | (#1)             | (#3)            |        | Still waiting f | or #3 to commit         |

|              |                 |           | Re     | egister sta      | itus            |        |                 |                         |

| F0 (#3)      | F2()            | F4 (      | ) F6(  | #6) F8           | 8 (#4) F        | 10 (#5 | i) F12          |                         |

| Still wait   | ing for #       | 3 #4 #5   | to com | mit              |                 |        |                 |                         |

| Entry #                 | Instru   | ıction    |                | Reorder sue     | ouffer<br>Exec | ute      | Write result  | Commit           |

|-------------------------|----------|-----------|----------------|-----------------|----------------|----------|---------------|------------------|

| 1                       | Load     | F6, 34(r  | 2) y           | es              | ye             | :S       | yes           | yes              |

| 2                       | Load     | F2, 45(r  | 3) y           | es              | ye             | s        | yes           | yes              |

| 3                       | Mul F    | ), F2, F  | 4 у            | es              | ye             | S        | yes           | yes              |

| 4                       | Sub F8   | 3, F6, F2 | 2 y            | es              | ye             | es       | yes           |                  |

| 5                       | Div F1   | 0, F0, F  | 6 у            | es              | ye             | :S       |               |                  |

| 6                       | Add F6   | ,F8,F2    | ye<br>Re       | es<br>servation | Station        | IS<br>IS | yes           |                  |

| Name                    | Busy     | Fm        | Vj             | Vk              | Qj             | Qk       | Cycl          | e after mul      |

| Add 1                   | no       |           |                |                 |                |          |               | vritten its      |

| Add2<br>Add3<br>Mul1    | no<br>no |           |                |                 |                |          | resul         | t and<br>nitted  |

|                         | no       | ъ.        | (110)          | (111)           |                |          | 0.00          | c #2 · · ·       |

| Mul2                    | yes      | Div       | (#3)           | (#1)            |                |          | Still waiting | for #3 to commit |

|                         |          |           | Re             | gister sta      | tus 🕢          |          |               |                  |

| F0 ()                   | F2()     | F4()      | F6(#6          | ) F8 (‡         | ‡4) F          | 10 (#5)  | F12           |                  |

| Still waiti<br>10/26/01 | ng for#  | 3,#4, #5  | to com<br>Reg. | mit<br>Renaming | CSE 471        | Autumn 0 | 1             | 17               |

```

Reorder buffer

Issue Execute

Entry # Instruction

Write result

Commit

Load F6, 34(r2) yes

Load F2, 45(r3) yes

yes

yes

yes

Mul F0, F2, F4 yes

yes

yes

yes

Sub F8, F6, F2 yes

yes

yes

yes

Div F10, F0, F6 yes

yes

Add F6,F8,F2 yes

Reservation Stations

Now #3 can

commit

Name Busy Fm Vj Vk Qj Qk

Add 1 no

Add2 no

Add3 no

Mul1 no

Mul2 yes Div (#3) (#1)

Register status

F0 () F2() F4 () F6(#6) F8 () F10 (#5) F12...

Still waiting for #4, #5 to commit

10/26/01 Reg. Renaming CSE 471 Autumn 01

```

| Entry #      | Instruction     |           | Is    | sue              | Execut          | e    | Write result                | Commit     |

|--------------|-----------------|-----------|-------|------------------|-----------------|------|-----------------------------|------------|

| 1            | Load            | F6, 34(r  | 2) y  | es               | yes             |      | yes                         | yes        |

| 2            | Load F2, 45(r3) |           |       | es               | yes             |      | yes                         | yes        |

| 3            | Mul F0, F2, F4  |           |       | es               | yes             |      | yes                         | yes        |

| 4            | Sub F8          | 8, F6, F2 | 2 y   | es               | yes             |      | yes                         | yes        |

| 5            | Div F1          | 0, F0, F  | 6 у   | es               | yes             |      |                             |            |

| 6            | Add Fe          | 5,F8,F2   | Re    | es<br>eservation | yes<br>Stations |      | yes                         |            |

| Name         | Busy            | Fm        | Vj    | Vk               | Qj              | Qk   | The next "in                | nteresting |

| Add 1        | no              |           |       |                  |                 |      | event is con                |            |

| Add2<br>Add3 | no<br>no        |           |       |                  |                 |      | of div; then<br>of #5, then |            |

| Mul1         | no              |           |       |                  |                 |      | of #6                       |            |

| Mul2         | yes             | Div       | (#3)  | (#1)             |                 |      |                             |            |

|              |                 |           | Re    | gister sta       | itus            |      |                             |            |

| F0 ()        | F2()            | F4()      | F6(#6 | ) F8 (           | F10 (#          | 5) I | F12                         |            |