### Principle of Locality: Memory Hierarchies

- · Text and data are not accessed randomly

- Temporal locality

- Recently accessed items will be accessed in the near future (e.g., code in loops, top of stack)

- Spatial locality

- Items at addresses close to the addresses of recently accessed items will be accessed in the near future (sequential code, elements of arrays)

- Leads to memory hierarchy at two main interface levels:

Processor Main memory -> Introduction of caches

- Main memory -> Introduction of caches

Main memory -> Secondary memory -> Virtual memory (paging systems)

Cache intro CSE 471 Autumn 01

# Processor - Main Memory Hierarchy Registers: Those visible to ISA + those renamed by hardware (Hierarchy of) Caches: plus their enhancements Write buffers, victim caches etc... TLB's and their management

- Virtual memory system (O.S. level) and hardware assists (page tables)

- Inclusion of information (or space to gather information) level per level

- Almost always true

Cache intro CSE 471 Autumn 01

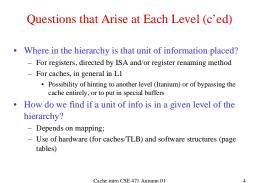

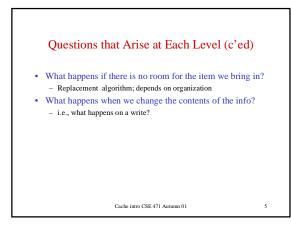

### Questions that Arise at Each Level

- What is the unit of information transferred from level to level ?

- Word (byte, double word) to/from a register

- Block (line) to/from cache

- $-\,$  Page table entry + misc. bits to/from TLB

- Page to/from disk

- When is the unit of information transferred from one level to a lower level in the hierarchy?

- Generally, on demand (cache miss, page fault)

- Sometimes earlier (prefetching)

Cache intro CSE 471 Autumn 01

3

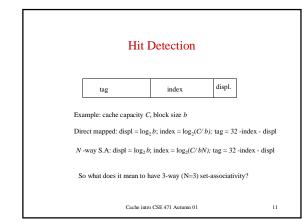

## Cache Organizations (c'ed)

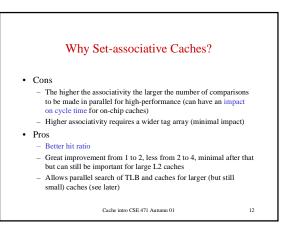

- · Set-associative cache.

- Blocks in the cache are grouped into sets and a given memory location (block) maps into a set. Within the set the block can be placed anywhere. Associativities of 2 (two-way set-associative), 3, 4,8 and even 16 have been implemented.

- Direct-mapped = 1-way set-associative

- Fully associative with m entries is m-way set associative

- Capacity

- Capacity = number of sets \* set-associativity \* block size

Cache intro CSE 471 Autumn 01

9

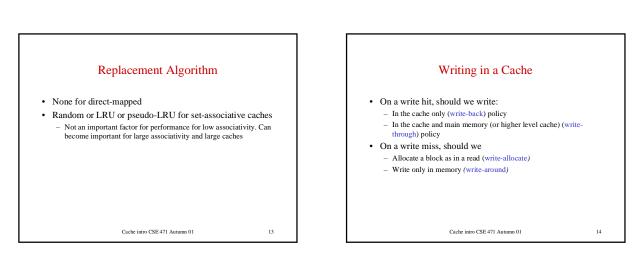

# The Main Write Options

- Write-through (aka store-through)

- $-\,$  On a write hit, write both in cache and in memory

- $-\,$  On a write miss, the most frequent option is write-around

- Pro: consistent view of memory (better for I/O); no ECC required for cache

- Con: more memory traffic (can be alleviated with write buffers)

- Write-back (aka copy-back)

- On a write hit, write only in cache (requires dirty bit)

- On a write miss, most often write-allocate (fetch on miss) but variations are possible

- Pro-con reverse of write through

Cache intro CSE 471 Autumn 01

15

- Compulsory misses (cold start)

- The first time you touch a block. Reduced (for a given cache capacity and associativity) by having large blocks

- Capacity misses

- The working set is too big for the ideal cache of same capacity and block size (i.e., fully associative with optimal replacement algorithm). Only remedy: bigger cache!

- Conflict misses (interference)

Mapping of two blocks to the same location. Increasing associativity decreases this type of misses.

- There is a fourth C: coherence misses (cf. multiprocessors)

16

Cache intro CSE 471 Autumn 01