## Xilinx AFX Board pinouts—1/21/03-- HWLAB

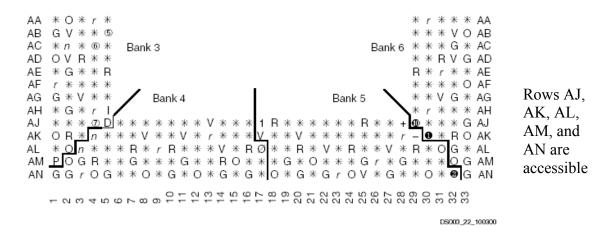

Figure 7: BG560 Pin Function Diagram

## **Pinout Diagrams**

The following diagrams, CS144 Pin Function Diagram, page 17 through FG680 Pin Function Diagram, page 27, illustrate the locations of special-purpose pins on Virtex FPGAs. Table 5 lists the symbols used in these diagrams. The diagrams also show I/O-bank boundaries.

| Symbol     | Pin Function                                                          |

|------------|-----------------------------------------------------------------------|

| *          | General I/O                                                           |

| *          | Device-dependent general I/O, n/c on<br>smaller devices               |

| V          | V <sub>CCINT</sub>                                                    |

| v          | Device-dependent V <sub>CCINT</sub> , n/c on smaller<br>devices       |

| 0          | Vcco                                                                  |

| R          | V <sub>REF</sub>                                                      |

| r          | Device-dependent V <sub>REF</sub> , remains I/O on<br>smaller devices |

| G          | Ground                                                                |

| Ø, 1, 2, 3 | Global Clocks                                                         |

Table 5: Pinout Diagram Symbols

Table 5: Pinout Diagram Symbols (Continued)

| Symbol             | Pin Function                       |

|--------------------|------------------------------------|

| O, O, Ø            | M0, M1, M2                         |

| 10, (1, (2,<br>(3, | D0/DIN, D1, D2, D3, D4, D5, D6, D7 |

| w,<br>4, 5, 6, 7   |                                    |

| В                  | DOUT/BUSY                          |

| D                  | DONE                               |

| Р                  | PROGRAM                            |

| I                  | INIT                               |

| К                  | CCLK                               |

| W                  | WRITE                              |

| S                  | CS                                 |

| Т                  | Boundary-scan Test Access Port     |

| +                  | Temperature diode, anode           |

| -                  | Temperature diode, cathode         |

| п                  | No connect                         |

Rows AJ, AK, AL, AM, and AN are accessible via the black plug-strips in front of the FPGA.