| ARM    |               |                           | Condition Codes |  |  |  |

|--------|---------------|---------------------------|-----------------|--|--|--|

|        |               |                           |                 |  |  |  |

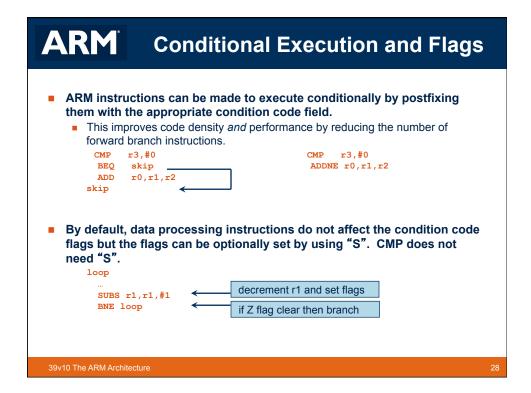

|        |               | codes are listed belo     |                 |  |  |  |

| Note A | L is the defa | ault and does not need to | be specified    |  |  |  |

|        |               |                           |                 |  |  |  |

|        | Suffix        | Description               | Flags tested    |  |  |  |

|        | EQ            | Equal                     | Z=1             |  |  |  |

|        | NE            | Not equal                 | Z=0             |  |  |  |

|        | CS/HS         | Unsigned higher or same   | C=1             |  |  |  |

|        | CC/LO         | Unsigned lower            | C=0             |  |  |  |

|        | MI            | Minus                     | N=1             |  |  |  |

|        | PL            | Positive or Zero          | N=0             |  |  |  |

|        | VS            | Overflow                  | V=1             |  |  |  |

|        | VC            | No overflow               | V=0             |  |  |  |

|        | HI            | Unsigned higher           | C=1 & Z=0       |  |  |  |

|        | LS            | Unsigned lower or same    | C=0 or Z=1      |  |  |  |

|        | GE            | Greater or equal          | N=V             |  |  |  |

|        | LT            | Less than                 | N!=V            |  |  |  |

|        | GT            | Greater than              | Z=0 & N=V       |  |  |  |

|        | LE            | Less than or equal        | Z=1 or N=!V     |  |  |  |

|        | AL            | Always                    |                 |  |  |  |

|        | _             |                           |                 |  |  |  |

|        |               |                           |                 |  |  |  |

| ARM                                                                          | Examples of conditional<br>execution |

|------------------------------------------------------------------------------|--------------------------------------|

| Use a sequence of severa                                                     | I conditional instructions           |

| if (a==0) func(1);                                                           |                                      |

| CMP r0,#0                                                                    |                                      |

| MOVEQ r0,#1                                                                  |                                      |

| BLEQ func                                                                    |                                      |

| if (a==0) x=0;<br>if (a>0) x=1;<br>CMP r0,#0<br>MOVEQ r1,#0<br>MOVGT r1,#1   |                                      |

| Use conditional compare<br>if (a==4    a==10) x<br>CMP r0,#4<br>CMPNE r0,#10 |                                      |

| MOVEQ r1,#0                                                                  |                                      |

| 39v10 The ARM Architecture                                                   | 30                                   |

| ARM                                                                                                                                                                                                                                                                                                                             | Dat                                 | a pro                                                      | cess                       | ing l                    | nstru | ictions |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|------------------------------------------------------------|----------------------------|--------------------------|-------|---------|

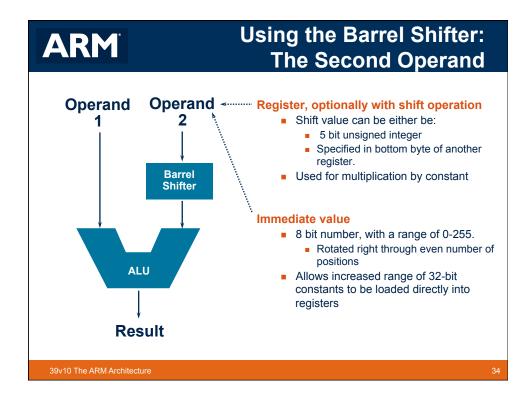

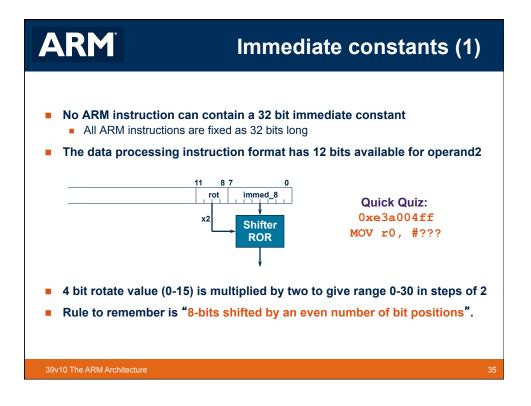

| <ul> <li>Consist of :         <ul> <li>Arithmetic:</li> <li>Logical:</li> <li>Comparisons:</li> <li>Data movement:</li> </ul> </li> <li>These instructions of Syntax:         <ul> <li>Syntax:</li> <li>Comparisons set Data movement:</li> <li>Second operand is set S</li></ul></li></ul> | cond>}<br>et flags or<br>t does not | MVN<br>k on regi<br>{S} Rd,<br>nly - they d<br>t specify R | Rn , Op<br>o not spec<br>n | TEQ<br>OT men<br>perand2 | RSB   | RSC     |

| 39v10 The ARM Architecture                                                                                                                                                                                                                                                                                                      |                                     |                                                            |                            |                          |       | 32      |

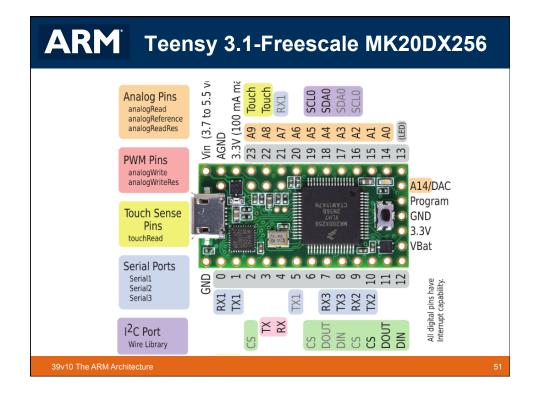

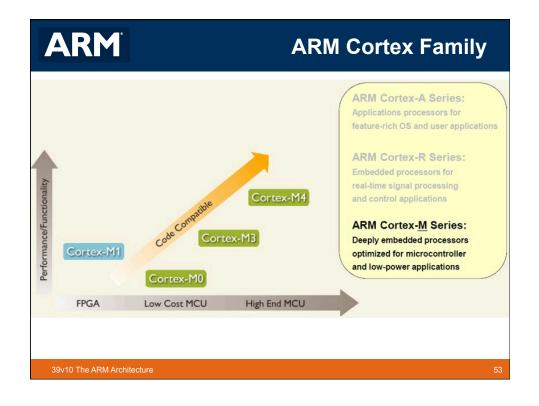

## ARM

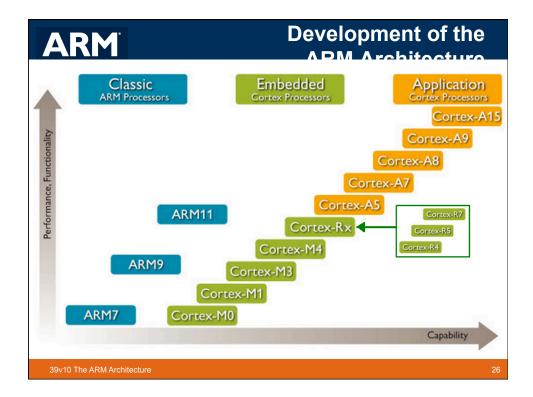

## **ARM Cortex Family**

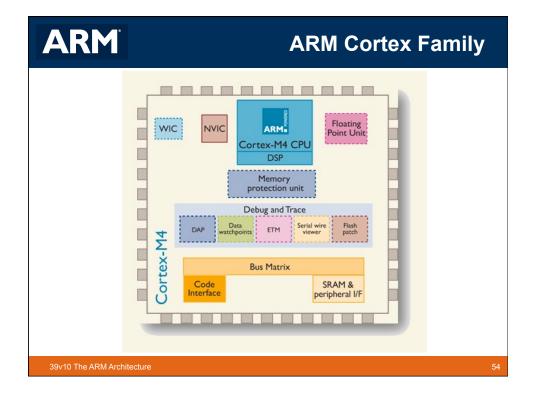

ARM Cortex-M4 Processor Microarchitecture

- Backwards compatible with ARM Cortex-M3

- New features

- Single cycle MAC (Up to 32 x 32 + 64 -> 64)

- DSP extensions

- Single Precision Floating Point Unit

Freescale IP and Innovation

- On-chip cache for instructions and data

- Cross-Bar Switch for concurrent multi-master/slave accessing

- On-chip DMA for CPU off-load

- Low-leakage Wake-up Unit adds flexibility for low power operation

- Architected for Digital Signal Processing

- Motor Control advanced algorithms, longer lifespan, power efficiency

- Automation high calculation and algorithm bandwidth at a low cost

- Power management designed for low/battery powered systems

- Audio and Video 5x performance improvement over software, making batteries last longer

39v10 The ARM Architecture

55