##

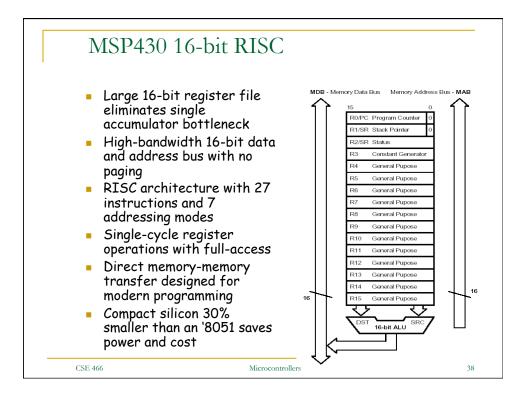

| 15 | BO - PC Program Counter<br>16-bit = no paging                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15 | R1 - SP Stack Pointer     Addressable = great "C" coc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 15 | v scgi scgi or cru gie N z c R2 - SR Status Register<br>Define LPM×                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

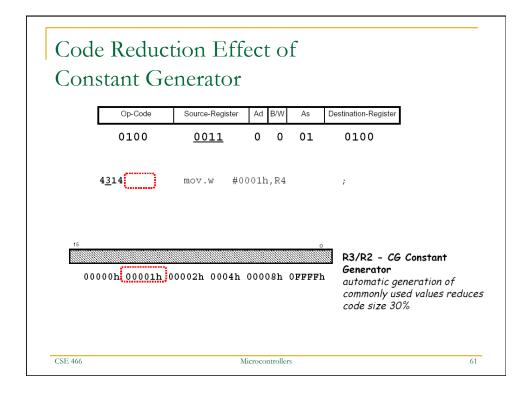

|    | 00002h 0004h 00008h OFFFFh<br>00002h 0004h 00008h OFFFFh<br>00008h 0008h 0008h OFFFFh<br>00008h 0008h |

| 15 | R4 - General Purpose                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 15 | <sub>0</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

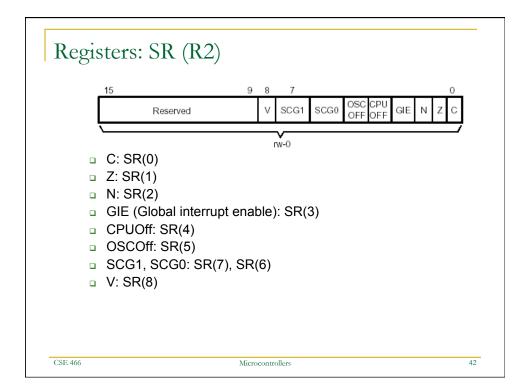

| tatus bits | Bit    | Description                                                                                 |                                                                                                                      |

|------------|--------|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| latus Dits | V      | Overflow bit. This bit is set when<br>overflows the signed-variable rang                    | the result of an arithmetic operation<br><sub>j</sub> e.                                                             |

|            |        | ADD(.B), ADDC(.B)                                                                           | Set when:<br>Positive + Positive = Negative<br>Negative + Negative = Positive,<br>otherwise reset                    |

|            |        | SUB(.B),SUBC(.B),CMP(.B)                                                                    | Set when:<br>Positive – Negative = Negative<br>Negative – Positive = Positive,<br>otherwise reset                    |

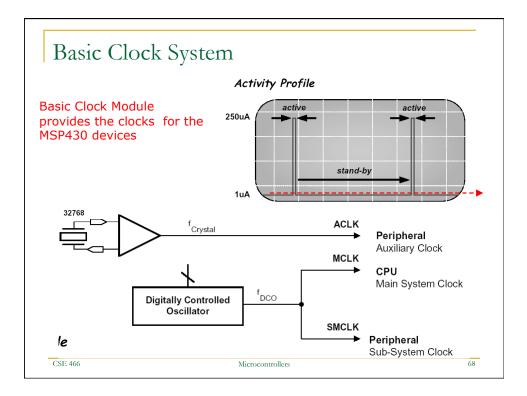

|            | SCG1   | System clock generator 1. This bit                                                          | , when set, turns off the SMCLK.                                                                                     |

|            | SCG0   | System clock generator 0. This t<br>generator, if DCOCLK is not used                        | oit, when set, turns off the DCO dc<br>for MCLK or SMCLK.                                                            |

|            | OSCOFF | Oscillator Off. This bit, when set, t<br>when LFXT1CLK is not use for M0                    | urns off the LFXT1 crystal oscillator,<br>CLK or SMCLK                                                               |

|            | CPUOFF | CPU off. This bit, when set, turns of                                                       | off the CPU.                                                                                                         |

|            | GIE    | General interrupt enable. This<br>interrupts. When reset, all maskab                        | bit, when set, enables maskable<br>le interrupts are disabled.                                                       |

|            | Ν      | Negative bit. This bit is set when t<br>is negative and cleared when the<br>Word operation: | he result of a byte or word operation<br>result is not negative.<br>N is set to the value of bit 15 of the<br>result |

|            |        | Byte operation:                                                                             | N is set to the value of bit 7 of the<br>result                                                                      |

|            | Z      | Zero bit. This bit is set when the re<br>and cleared when the result is not                 | esult of a byte or word operation is 0<br>0.                                                                         |

|            | С      | Carry bit. This bit is set when the<br>produced a carry and cleared whe                     | e result of a byte or word operation<br>n no carry occurred.                                                         |

|                 | uraa ragiat   |         |            | do in the instructio                    |

|-----------------|---------------|---------|------------|-----------------------------------------|

| ls – sc<br>/ord | burce registe | er addi | ressing mo | ode in the instruction                  |

|                 | Register      | As      | Constant   | Remarks                                 |

|                 | R2            | 00      |            | Register mode                           |

|                 | R2            | 01      | (0)        | Absolute address mode                   |

|                 | R2            | 10      | 00004h     | +4, bit processing                      |

|                 | R2            | 11      | 00008h     | +8, bit processing                      |

|                 | R3            | 00      | 00000h     | 0, word processing                      |

|                 | R3            | 01      | 00001h     | +1                                      |

|                 | R3            | 10      | 00002h     | +2, bit processing                      |

|                 | R3            | 11      | 0FFFFh     | <ul> <li>–1, word processing</li> </ul> |

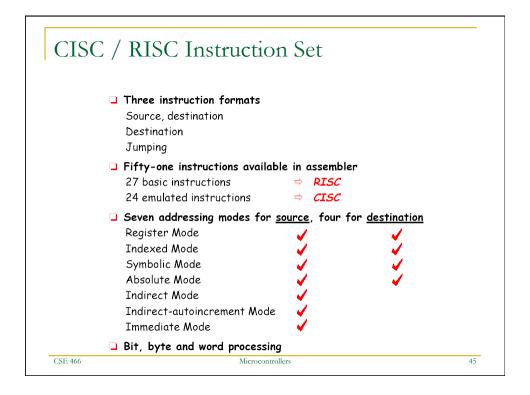

| Format I            | Format II      | Format III      |

|---------------------|----------------|-----------------|

| Source, Destination | Single Operand | +/- 9bit Offset |

| add(.b)             | call           | jmp             |

| addc(.b)            | swpb           | jc              |

| and(.b)             | sxt            | jnc             |

| bic(.b)             | push(.b)       | jeq             |

| bis(.b)             | reti           | jne             |

| bit(.b)             | rra(.b)        | jge             |

| cmp(.b)             | rrc(.b)        | j1              |

| dadd(.b)            |                | jn              |

| mov(.b)             |                |                 |

| sub(.b)             |                |                 |

| subc(.b)            |                |                 |

| xor(.b)             |                |                 |

| otal Instruc        | tions          |                 |         |

|---------------------|----------------|-----------------|---------|

|                     |                |                 |         |

| Format I            | Format II      | Format III      | Support |

| Source, Destination | Single Operand | +/- 9bit Offset |         |

| add(.b)             | br             | jmp             | clrc    |

| addc(.b)            | call           | jc              | setc    |

| and(.b)             | swpb           | jnc             | clrz    |

| bic(.b)             | sxt            | jeq             | setz    |

| bis(.b)             | push(.b)       | jne             | clrn    |

| bit(.b)             | pop.(b)        | jge             | setn    |

| cmp(.b)             | rra(.b)        | jl              | dint    |

| dadd(.b)            | rrc(.b)        | jn              | eint    |

| mov(.b)             | inv(.b)        |                 | nop     |

| sub(.b)             | inc(.b)        |                 | ret     |

| subc(.b)            | incd(.b)       |                 | reti    |

| xor(.b)             | dec(.b)        |                 |         |

|                     | decd(.b)       |                 |         |

|                     | adc (b)        |                 |         |

|                     | sbc(.b)        |                 |         |

|                     | clr(.b)        |                 |         |

|                     | dadc(.b)       |                 |         |

|                     | rla(.b)        |                 |         |

|                     | rlc(.b)        |                 |         |

|                     | tst(.b)        |                 |         |

|          |                   | l instruct                     |                                               | 15     |    |    |      |         |   |

|----------|-------------------|--------------------------------|-----------------------------------------------|--------|----|----|------|---------|---|

| 15 14 13 | 3 12 <sup>-</sup> | 1 10 9 8                       | 7                                             | 6      | 5  | 4  | 3    | 2       | 1 |

| Op-coc   |                   | S-Reg                          | Ad                                            | B/W    |    | As |      | D-Re    | g |

| Mnemonic | S-Reg,            | Operation                      |                                               |        |    |    | Stat | tus Bit | s |

|          | D-Reg             |                                |                                               |        |    | v  | Ν    | z       | с |

| MOV(.B)  | src,ds            | src $\rightarrow$ dst          |                                               |        |    | _  | -    | _       | _ |

| ADD(.B)  | src,ds            | src + dst $\rightarrow$ dst    | src + dst $\rightarrow$ dst                   |        |    | *  | *    | *       | * |

| ADDC(.B) | src,ds            | src + dst + C $\rightarrow$ d  | $\text{src + dst + C} \rightarrow \text{dst}$ |        |    | *  | *    | *       | * |

| SUB(.B)  | src,ds            | dst + .not.src + 1             | dst + .not.src + 1 $\rightarrow$ dst          |        |    | *  | *    | *       | * |

| SUBC(.B) | src,ds            | dst + .not.src + C             | dst + .not.src + C $\rightarrow$ dst          |        |    | *  | *    | *       | * |

| CMP(.B)  | src,ds            | dst – src                      |                                               |        |    | *  | *    | *       | * |

| DADD(.B) | src,ds            | src + dst + C $\rightarrow$ d  | st (de                                        | cimall | y) | *  | *    | *       | * |

| BIT(.B)  | src,ds            | src .and. dst                  |                                               |        |    | 0  | *    | *       | * |

| BIC(.B)  | src,ds            | .not.src .and. dst             | $\rightarrow$ ds                              | t      |    | _  | -    | _       | - |

| BIS(.B)  | src,ds            | src .or. dst $\rightarrow$ dst |                                               |        |    | _  | _    | _       | - |

| XOR(.B)  | src,ds            | src .xor. dst $\rightarrow$ ds | t                                             |        |    | *  | *    | *       | * |

| AND(.B)  | src,dst           | src .and. dst $\rightarrow$ ds | st                                            |        |    | 0  | *    | *       | * |

| 15 14 -  | 3 12 11         | 10 9 8 7                                             | 6 5 | 4  | 3           | 2     | 1  |

|----------|-----------------|------------------------------------------------------|-----|----|-------------|-------|----|

|          | Op-co           | ode E                                                | 3/W | ٩d |             | D/S-R | eg |

| Mnemonic | S-Reg,<br>D-Reg | Operation                                            |     | v  | us Bit<br>N | z     | с  |

|          | -               |                                                      |     | -  |             | _     | -  |

| RRC(.B)  | dst             | $C \to MSB \to \dots \dots LSB \to 0$                | С   | *  | *           | *     | *  |

| RRA(.B)  | dst             | $MSB \to MSB \to \dots LSB \to$                      | → C | 0  | *           | *     | *  |

| PUSH(.B) | src             | SP – 2 $ ightarrow$ SP, src $ ightarrow$ @SI         | Р   | -  | -           | -     | -  |

| SWPB     | dst             | Swap bytes                                           |     | -  | -           | _     | -  |

| CALL     | dst             | $SP - 2 \rightarrow SP, PC+2 \rightarrow @$          | 0SP | _  | _           | _     | _  |

|          |                 | $dst \to \text{PC}$                                  |     |    |             |       |    |

|          |                 | TOS $\rightarrow$ SR, SP + 2 $\rightarrow$ SF        | D   | *  | *           | *     | *  |

| RETI     |                 |                                                      |     |    |             |       |    |

| RETI     |                 | $TOS \rightarrow PC, SP \textbf{+} 2 \rightarrow SP$ | )   |    |             |       |    |

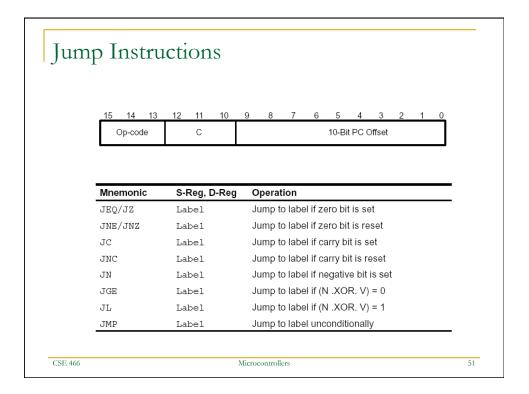

| 10 11 00 110    | n Formats                                            | 5          |                              |                       |     |

|-----------------|------------------------------------------------------|------------|------------------------------|-----------------------|-----|

| ; Format I      | Source and Des                                       | tinatio    | n                            |                       |     |

| Op-Code         | Source-Register                                      | Ad B/W     | As                           | Destination-Register  |     |

| 5405<br>5445    | add.w R4,<br>add.b R4,                               |            |                              | ; R4+R5=R5 ; R4+R5=R5 |     |

| ; Format I      | Destination C                                        | mly<br>B/W | Ad                           | D/S- Register         |     |

|                 |                                                      |            |                              |                       |     |

| 6404<br>6444    | rlc.w R4<br>rlc.b R4                                 | 1          |                              | ;<br>;                |     |

| 6444            | rlc.w R4                                             | Un) cond   | itiona                       | ;<br>;<br>al Jumps    |     |

| 6444            | rlc.w R4<br>rlc.b R4                                 | -          | <b>ition</b> a<br>bit PC off | -                     |     |

| 6444 ; Format I | rlc.w R4<br>rlc.b R4<br>II There are 8(<br>Condition | -          |                              | -                     | p_1 |

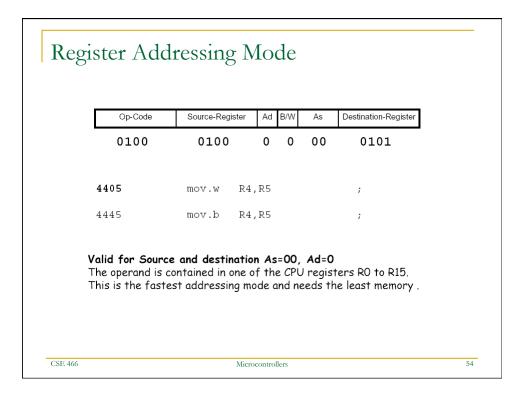

| As/Ad | Addressing Mode           | Syntax | Description                                                                                                                          |

|-------|---------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------|

| 00/0  | Register mode             | Rn     | Register contents are operand                                                                                                        |

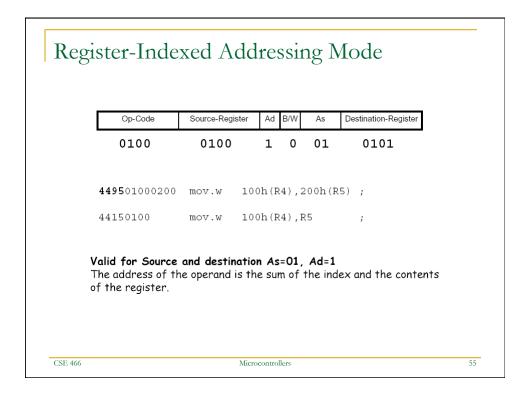

| 01/1  | Indexed mode              | X(Rn)  | (Rn + X) points to the operand. X is stored in the next word.                                                                        |

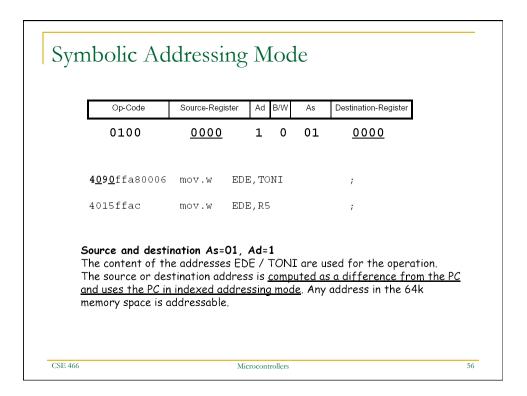

| 01/1  | Symbolic mode             | ADDR   | (PC + X) points to the operand. X<br>is stored in the next word. Indexed<br>mode X(PC) is used.                                      |

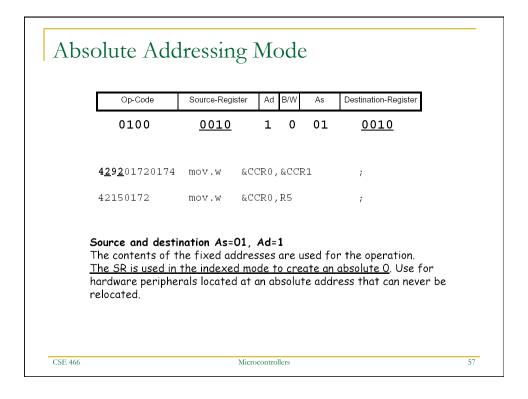

| 01/1  | Absolute mode             | &ADDR  | The word following the instruction<br>contains the absolute address. X<br>is stored in the next word. Indexed<br>mode X(SR) is used. |

| 10/—  | Indirect register<br>mode | @Rn    | Rn is used as a pointer to the operand.                                                                                              |

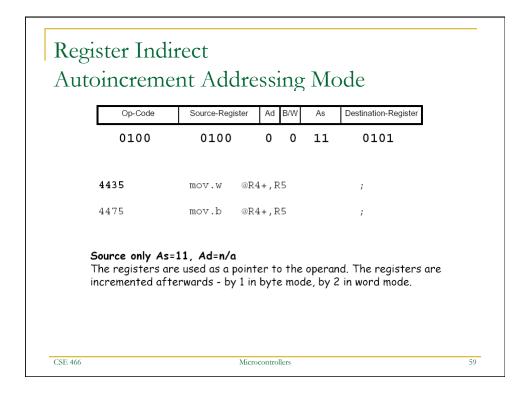

| 11/—  | Indirect<br>autoincrement | @Rn+   | Rn is used as a pointer to the operand. Rn is incremented afterwards by 1 for .B instructions and by 2 for .W instructions.          |

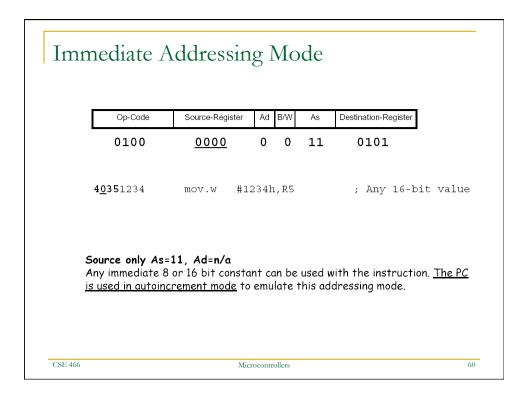

| 11/—  | Immediate mode            | #N     | The word following the instruction<br>contains the immediate constant<br>N. Indirect autoincrement mode<br>@PC+ is used.             |

| Op-Code        | Source-Register   | Ad B/W    | As | Destination-Register        |

|----------------|-------------------|-----------|----|-----------------------------|

| 0100           | 0100              | 0 0       | 10 | 0101                        |

|                |                   |           |    |                             |

| 4425           | mov.w @R          | 4,R5      |    | ;                           |

| 4465           | mov.b @R          | 4,R5      |    | ;                           |

| The indexed mo | re used as a poin | ex may be |    | d.<br>or "indirect register |

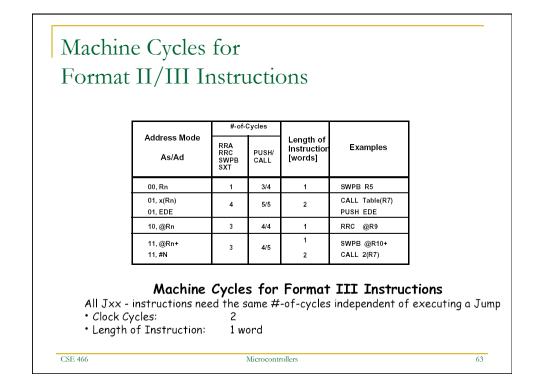

|   | y crec       |               | 1 0111      |                                  | structions      |  |

|---|--------------|---------------|-------------|----------------------------------|-----------------|--|

| ] | Addre:<br>As | ss Mode<br>Ad | #-of-Cycles | Length of<br>Instruction [words] | Examples        |  |

|   |              | 0, Rm         | 1           | 1                                | MOV R5,R8       |  |

|   | 00, Rn       | 0, PC         | 2           | 1                                | BR R9           |  |

|   |              | 1, x(Rm)      |             |                                  | ADD R5,2(R6)    |  |

|   | 00, Rn       | 1, EDE        | 4           | 2                                | XOR R8,EDE      |  |

|   |              | 1,&EDE        |             |                                  | MOV R5,&EDE     |  |

|   | 01,x(Rn)     | 0, Rm         |             |                                  | MOV 2(R5),R7    |  |

|   | 01, EDE      | 0, RM         | 3           | 2                                | AND EDE,R6      |  |

|   | 01,x(Rn)     | 1,x(Rm)       |             |                                  | ADD 4(R4),6(R9) |  |

|   | 01,EDE       | 1,TONI        | 6           | 3                                | CMP EDE, TONI   |  |

|   | 01,&EDE      | 1,&EDE        |             |                                  | MOV R5,&EDE     |  |

|   | 10,@Rn       | 0, Rm         | 2           | 1                                | AND @R4,R5      |  |

|   |              | 1,x(Rm)       |             |                                  | XOR @R5,8(R6)   |  |

|   | 10,@Rn       | 1, EDE        | 5           | 2                                | MOV @R5,EDE     |  |

|   |              | 1,&EDE        |             |                                  | XOR @R5,&EDE    |  |

|   | 11.@Rn+      | 0,Rm          | 2           | 1                                | ADD @R5+,R6     |  |

|   | ,0           | 0, PC         | 3           | 1                                | BR @R5+         |  |

|   | 11,#N        | 0,Rm          | 2           | 2                                | MOV #20,R9      |  |

|   |              | 0,PC          | 3           |                                  | BR #2AEh        |  |

|   | 11,@Rn+      | 1,x(Rm)       |             | 2                                | MOV @R9+,2(R4)  |  |

|   | 11,#N        | 1,EDE         | 5           | 3                                | ADD #33,EDE     |  |

|   | 11,@Rn+      | 1,&EDE        | 5           | 2                                | MOV @R9+,&EDE   |  |

|   | 11,#N        |               |             | 3                                | ADD #33,&EDE    |  |