|                       | Address        | Labels  | Code       |                        | Comments                                                          |

|-----------------------|----------------|---------|------------|------------------------|-------------------------------------------------------------------|

|                       | \$000          | Daberto | 1mp        | RESET                  | / Reset Handler                                                   |

|                       | \$002          |         | jmp        | EXT INTO               | ; IRQO Handler                                                    |

|                       | \$0.04         |         | jmp        | EXT_INT1               | ; IRQ1 Handler                                                    |

| Fixed location        | \$006          |         | jmp        | TIM2_COMP              | ; Timer2 Compare Handler                                          |

|                       | \$008          |         | jmp        | TIM2_OVF               | ; Timer2 Overflow Handler                                         |

| in memory to find     | \$00A          |         | jmp        | TIM1_CAPT              | ; Timerl Capture Handler                                          |

| in memory to find     | \$00C          |         | jmp        | TIM1_COMPA             | ; Timerl CompareA Handler                                         |

| first instruction for | \$00E<br>\$010 |         | jmp        | TIM1_COMPB<br>TIM1_OVF | ; Timerl CompareB Handler<br>; Timerl Overflow Handler            |

|                       | \$012          |         | jmp<br>1mp | TIMI_OVF               | ; TimerO Overflow Handler                                         |

| each type of          | \$014          |         | jmp        | SPI STC                | ; SPI Transfer Complete Handler                                   |

| • •                   | \$016          |         | jmp        | USART RXC              | / USART RX Complete Handler                                       |

| interrupt             | \$018          |         | jmp        | USART_UDRE             | ; UDR Empty Handler                                               |

| ·                     | \$01A          |         | jmp        | USART_TXC              | ; USART TX Complete Handler                                       |

| Only room for one     | \$01C          |         | jmp        | ADC                    | ; ADC Conversion Complete Handler                                 |

|                       | \$01E          |         | jmp        | EE_RDY                 | ; EEPROM Ready Handler                                            |

| instruction           | \$020          |         | jmp        | ANA_COMP<br>TWSI       | ; Analog Comparator Handler<br>; Two-wire Serial Interface Handle |

|                       | \$022<br>\$024 |         | jmp<br>1mp | EXT INT2               | ; NWO-WIFE SETIAL INTEFFACE Handle<br>; IRO2 Handler              |

| JMP to location       | \$024          |         | 1mp        | TIMO COMP              | ; Timer0 Compare Handler                                          |

| of complete ISR       | \$028          |         | 1mp        | SPM RDY                | ; Store Program Memory Ready Handle                               |

| or complete ISIX      | ,              |         |            | -                      |                                                                   |

|                       | \$02A          | RESET : | ldi        | r16, high (RAMEND)     | ; Main program start                                              |

|                       | \$02B          |         | out        | SPH,r16                | ; Set Stack Pointer to top of RAM                                 |

|                       | \$02C          |         | ldi        | r16,low(RAMEND)        |                                                                   |

|                       | \$02D          |         | out        | SPL, r16               |                                                                   |

|                       | \$02E<br>\$02F |         | sei        | r> xxx                 | ; Enable interrupts                                               |

|                       | \$02F          |         | <118       | .1> XXX                |                                                                   |

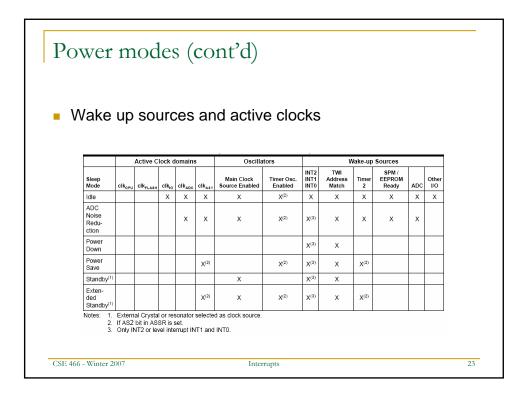

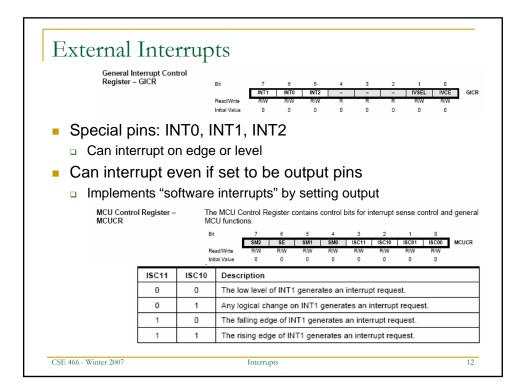

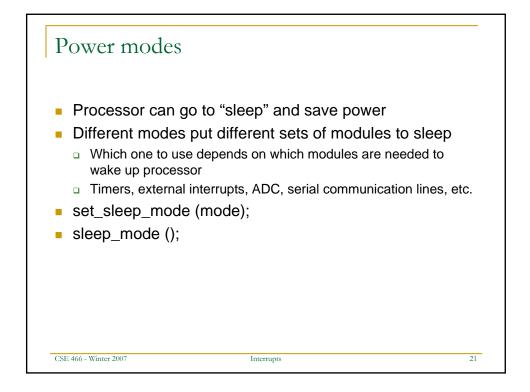

| MCU Control Register –<br>MCUCR | The MCU Control Register contains control bits for power management.   Bit 7 0 5 4 3 2 1 0 Mcucr   ReadWine SM2 SE SM1 SM0 ISC11 ISC11 ISC01 < |     |     |                                 |  |  |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|---------------------------------|--|--|

|                                 | SM2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | SM1 | SM0 | Sleep Mode                      |  |  |

|                                 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0   | 0   | ldle                            |  |  |

|                                 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0   | 1   | ADC Noise Reduction             |  |  |

|                                 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1   | 0   | Power-down                      |  |  |

|                                 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1   | 1   | Power-save                      |  |  |

|                                 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0   | 0   | Reserved                        |  |  |

|                                 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0   | 1   | Reserved                        |  |  |

|                                 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1   | 0   | Standby <sup>(1)</sup>          |  |  |

|                                 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1   | 1   | Extended Standby <sup>(1)</sup> |  |  |

|                                 | Note: 1. Standby mode and Extended Standby mode are only available with external crystals<br>or resonators.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |     |                                 |  |  |

|                                 | Bit 6 – SE: Sleep Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |     |                                 |  |  |

|                                 | The SE bit must be written to logic one to make the MCU enter the sleep mode when the<br>SLEEP instruction is executed. To avoid the MCU entering the sleep mode unless it is<br>the programmers purpose, it is recommended to write the Sleep Enable (SE) bit to one<br>just before the execution of the SLEEP instruction and to clear it immediately after wak-<br>ing up.                                                                                                                                                                                          |     |     |                                 |  |  |