## Memory Mapped IO

(and the CerfBoard)

## The problem

- How many IO pins are available on the 8051?

- What if you are using interrupts, serial, etc...?

- We want a consistent interface to I/O devices

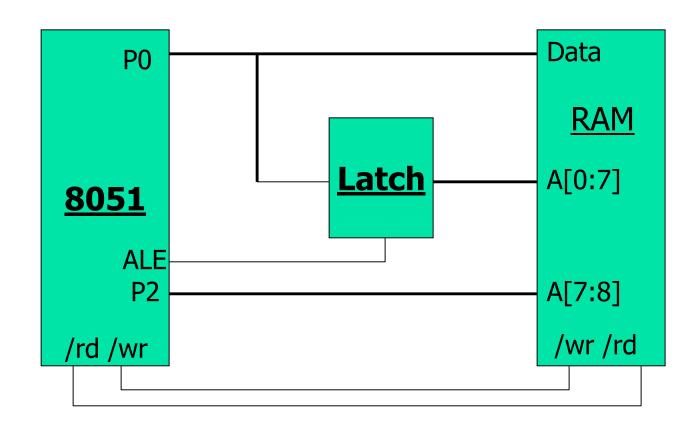

## **External Data Memory**

1 4k byte RAM chip

#### <sub>n</sub> Interface:

- Bi-directional data bus

- Address bus. How big?

- n /wr and /rd

- n /ce = Chip Enable

### The 8051 interface

- P0 does double duty

- When ALE is high, P0 is the lower 8 bits of the address

- When it's low, P0 is the data bus

- We need a latch

$$_{n}$$

P3.6 = /wr

$$_{n}$$

P3.7 = /rd

## **Block Diagram**

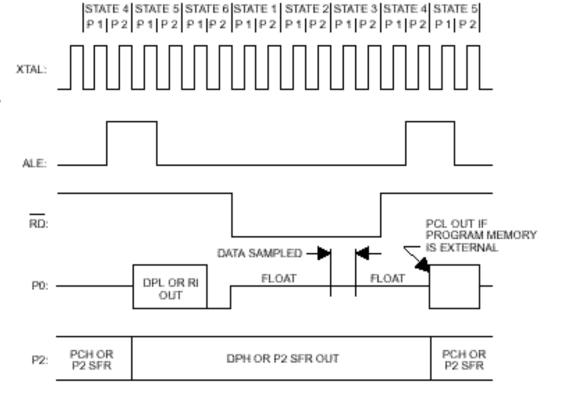

## External Data Memory Read

ALE's falling edge Latches the address

When /rd is low the Data bus must be stable

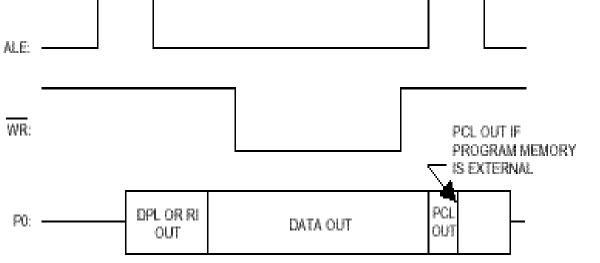

## **External Data Memory Write**

STATE 4 STATE 5 STATE 6 STATE 1 STATE 2 STATE 3 STATE 4 STATE 5 P 1 P 2 P 1 P 2 P 1 P 2 P 1 P 2 P 1 P 2 P 1 P 2

ALE's falling edge Latches the address

Data output is stable While /wr is low

### The Software Side

#### Use the MOVX instruction to access external data memory

MOV R0, #external\_address MOVX A,@R0 # uses only 8-bit address for external RAM

#### <u>Or</u>

MOV DPL, #external\_address\_high MOV DPH, #external\_address\_low MOVX A, @DPTR;

## Hooking up I/O Devices

- Why not put I/O stuff in the address space?

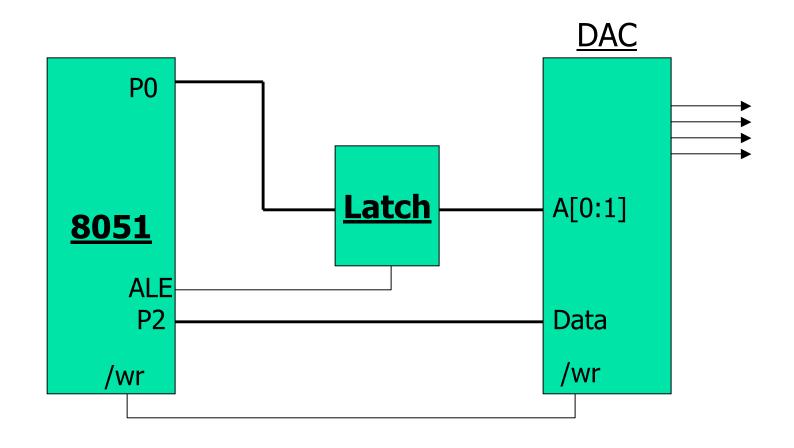

- Let's hook up a DAC (Digital to Analog Converter)

- 4 analog outputs (address bits?)

- <sub>n</sub> 8 data bits

- We can only write to it

## **Block Diagram**

## Memory Mapped I/O

n How do we use it?

```

MOV A, 45 ; what we want to send

```

```

MOV R0, 1 ; select output #2

```

```

MOVX @R0, A ; write it

```

n What if we did:

- <sub>n</sub> MOV R0, 4

- What output will we write to?

### More devices

- n More DACs

- n RAM

- ADC (Analog to Digital)

- n LCD

- n Keyboards

- More IO pins

- Disk drives

## The CerfBoard

# Overview

- StrongARM 1100 processor

- <sub>n</sub> 200mhz

- Ethernet, USB

- 32MB RAM, 16meg Flash ROM

- Compact Flash slot

- n 3 RS232 Serial Ports (one for console)

- <sub>n</sub> 16 GPIO pins

## Memory Mapped I/O

- Lots of devices are memory mapped on the CerfBoard

- GPIO registers

- Power Management Registers

- Serial Registers

- Interrupt Control Registers

- Compact Flash