### Lecture 12

- Logistics

- HW4 due today

- Last lecture

- Timing diagrams

- Hazards

- Today

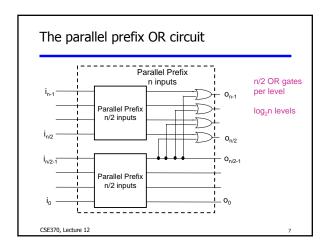

- Time/space trade offs: Parallel prefix trees

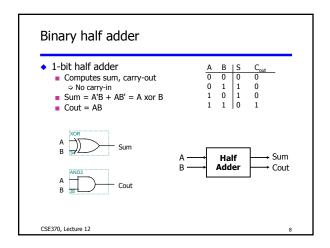

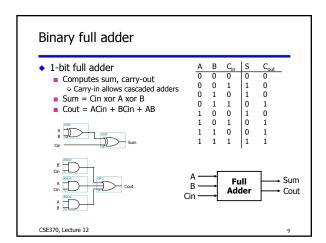

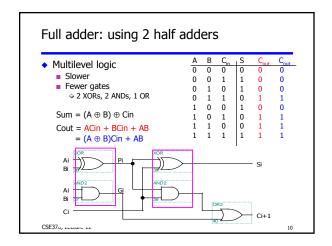

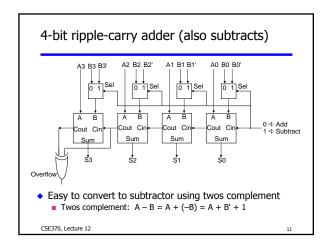

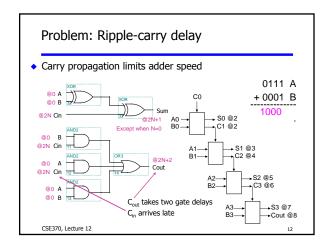

- Adders

- The conclusion of combinational logic!!!

CSE370, Lecture 12

## The "WHY" slide

- Timing/space trade offs

- In real life, complex logic circuits you will work on will not have one minimum circuit. You will have to learn to understand what parameters to optimize your design on, and be able to come up with "trade offs" suitable for your application or customer's needs.

- Adders

- Arithmetic logic units (ALUs) such as adders and multipliers perform most computer instructions. Therefore, it is critical to know how they works, how they scale, and how they may be optimized for time/space.

CSE370, Lecture 12

# What do we mean by time/speed tradeoff?: Linear chains vs. trees

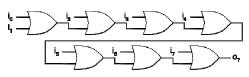

Lets say we want to implement an 8-input OR function with only 2-input gates

Gates: 7 Max delay: 7

CSE370, Lecture 12

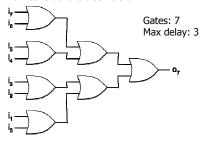

### Linear chains vs. trees

Now consider the tree version

CSE370, Lecture 12

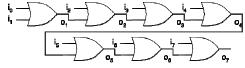

### And now we change the problem slightly

Build a circuit that takes 8 single bit inputs and calculates the OR of the first 2, the OR of the first 3, the OR of the first 4, and so on, up to the OR of all 8

Gates: 7 Max delay: 7

CSE370, Lecture 12

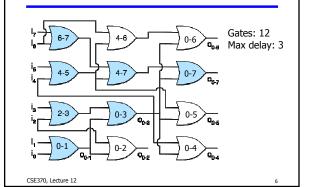

### A parallel version of the prefix circuit

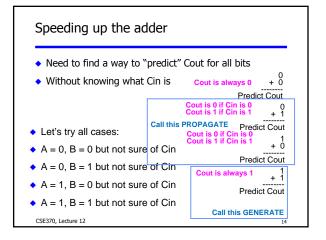

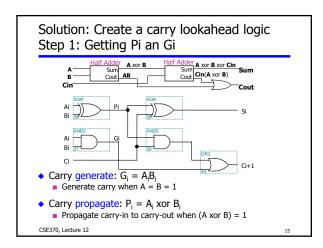

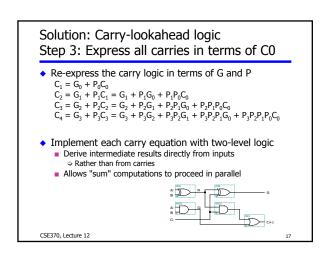

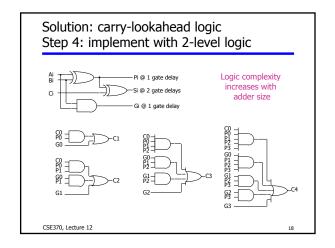

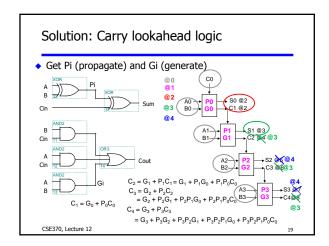

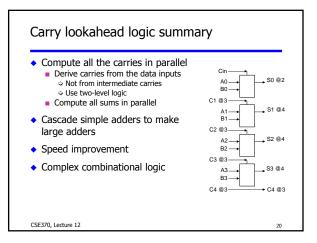

# Can we be clever and speed this up? Let's compute all the carries in parallel Derive carries from the data inputs Not from intermediate carries Use two-level logic Compute all sums in parallel How do we do that???

### We've finished combinational logic...

- Negative numbers in binary

- Truth tables

- Basic logic gates

- Schematic diagrams

- Minterm and maxterm expansions (canonical, minimized)

- de Morgan's theorem

- AND/OR to NAND/NOR logic conversion

- K-maps, logic minimization, don't cares

- Multiplexers/demultiplexers

- PLAs/PALs

- ROMs

- Multi-level logics

- Timing diagrams

- Hazards

- Adders

CSE370, Lecture 12

1