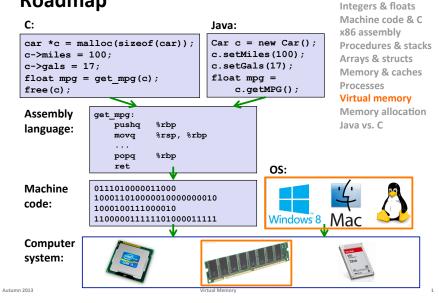

### Roadmap

University of Washington

Memory & data

# **Virtual Memory (VM)**

- Overview and motivation

- VM as tool for caching

- Address translation

- VM as tool for memory management

- VM as tool for memory protection

#### **Again: Processes**

- Definition: A process is an instance of a running program

- One of the most important ideas in computer science

- Not the same as "program" or "processor"

- Process provides each program with two key abstractions:

- Logical control flow

- Each process seems to have exclusive use of the CPU

- Private virtual address space

- Each process seems to have exclusive use of main memory

- How are these illusions maintained?

- Process executions interleaved (multi-tasking) done...

- Address spaces managed by virtual memory system now!

Autumn 2013

Virtual Memory

University of Washing

### Memory as we know it so far... is virtual!

Programs refer to virtual memory addresses

FF·····

- movl (%ecx),%eax

- Conceptually memory is just a very large array of bytes

- Each byte has its own address

- System provides address space private to particular "process"

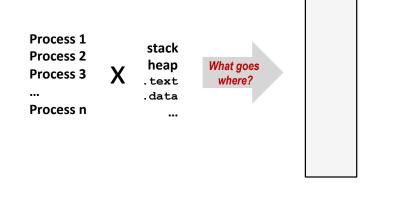

- Allocation: Compiler and run-time system

- Where different program objects should be stored

- All allocation within single virtual address space

- But...

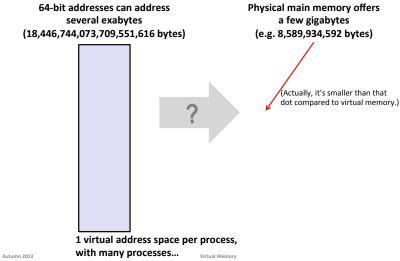

- We probably don't have exactly 2<sup>w</sup> bytes of physical memory.

- We certainly don't have 2<sup>w</sup> bytes of physical memory for every process.

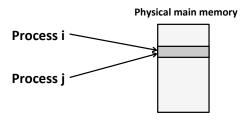

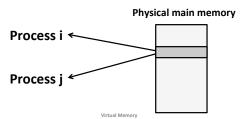

- We have multiple processes that usually should not interfere with each other, but sometimes should share code or data.

Autumn 2013 Virtual Memory 3 Autumn 2013

Virtual Memory

# **Problem 1: How Does Everything Fit?**

5 Autumn 2013 Virtual Memory

#### **Problem 3: How To Protect**

### **Problem 4: How To Share?**

Autumn 2013

# **Problem 2: Memory Management**

Physical main memory

# How can we solve these problems?

#### Indirection

- "Any problem in computer science can be solved by adding another level of indirection." —David Wheeler, inventor of the subroutine (a.k.a. procedure)

- Without Indirection Name Thing

- With Indirection Name Thing

What if I want to move Thing?

Autumn 2013 Virtual Memory

University of Washington

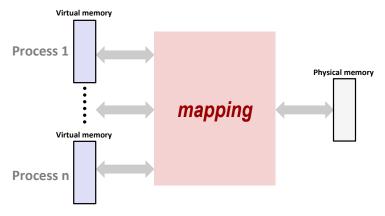

# **Indirection in Virtual Memory**

- Each process gets its own private virtual address space

- Solves the previous problems

#### **Indirection**

- Indirection: the ability to reference something using a name, reference, or container instead the value itself. A flexible mapping between a name and a thing allows changing the thing without notifying holders of the name.

- Without Indirection Name Thing

- With Indirection

Name

Thing

Examples of indirection:

- Domain Name Service (DNS): translation from name to IP address

- phone system: cell phone number portability

- snail mail: mail forwarding

- 911: routed to local office

- Dynamic Host Configuration Protocol (DHCP): local network address assignment

- call centers: route calls to available operators, etc.

Virtual Mamoru

lemory

# **Address Spaces**

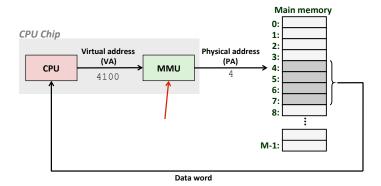

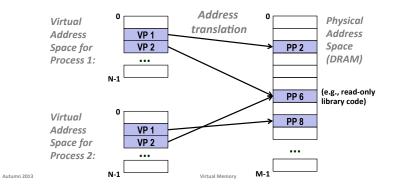

- Virtual address space: Set of N = 2<sup>n</sup> virtual addresses {0, 1, 2, 3, ..., N-1}

- Physical address space: Set of M = 2<sup>m</sup> physical addresses (n >= m) {0, 1, 2, 3, ..., M-1}

- Every byte in main memory has:

- one physical address

- zero, one, or more virtual addresses

Autumn 2013

Virtual Memory

11

Autumn 2013

Virtual Memory

### **Mapping**

Autumn 2013

Virtual Memory

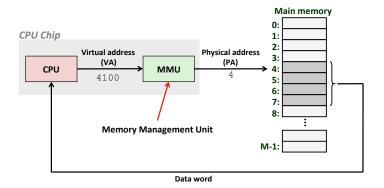

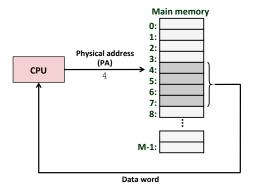

# A System Using Virtual Addressing

- Physical addresses are completely invisible to programs.

- Used in all modern desktops, laptops, servers, smartphones...

- One of the great ideas in computer science

# A System Using Physical Addressing

#### Used in "simple" systems with (usually) just one process:

embedded microcontrollers in devices like cars, elevators, and digital picture frames

Autumn 2013 Virtual Memory

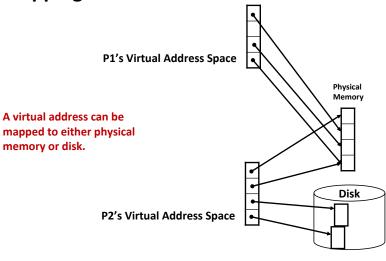

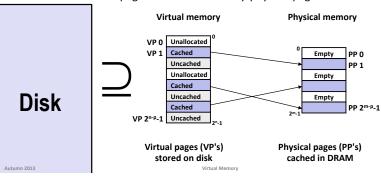

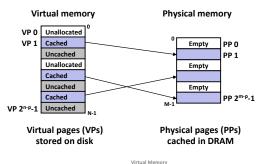

# Why Virtual Memory (VM)?

#### Efficient use of limited main memory (RAM)

- Use RAM as a cache for the parts of a virtual address space

- some non-cached parts stored on disk

- some (unallocated) non-cached parts stored nowhere

- Keep only active areas of virtual address space in memory

- transfer data back and forth as needed

#### Simplifies memory management for programmers

Each process gets the same full, private linear address space

#### Isolates address spaces

- One process can't interfere with another's memory

- because they operate in different address spaces

- User process cannot access privileged information

- different sections of address spaces have different permissions

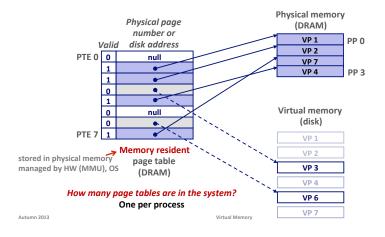

### VM and the Memory Hierarchy

- Think of virtual memory as array of N = 2<sup>n</sup> contiguous bytes.

- Pages of virtual memory are usually stored in physical memory, but sometimes spill to disk.

- Pages are another unit of aligned memory (size is P = 2<sup>p</sup> bytes)

- Each virtual page can be stored in any physical page.

University of Washington

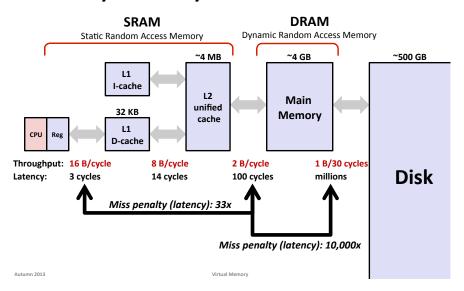

### **Memory Hierarchy: Core 2 Duo**

Not drawn to scale

### or: Virtual Memory as DRAM Cache for Disk

- Think of virtual memory as an array of N = 2<sup>n</sup> contiguous bytes stored on a disk.

- Then physical main memory is used as a cache for the virtual memory array

- The cache blocks are called pages (size is P = 2<sup>p</sup> bytes)

Autumn 2013 Virtual Memory

University of Washing

# **Virtual Memory Design Consequences**

- Large page size: typically 4-8 KB, sometimes up to 4 MB

- Fully associative

- Any virtual page can be placed in any physical page

- Requires a "large" mapping function different from CPU caches

- Highly sophisticated, expensive replacement algorithms in OS

- Too complicated and open-ended to be implemented in hardware

- Write-back rather than write-through

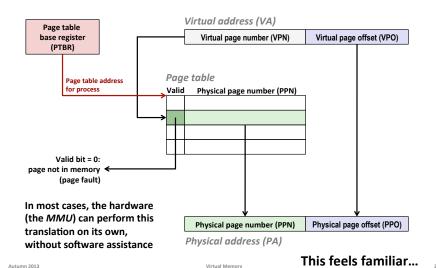

#### **Address Translation**

How do we perform the virtual -> physical address translation?

Autumn 2013 Virtual Memory 21

**University of Washington**

# **Address Translation With a Page Table**

### **Address Translation: Page Tables**

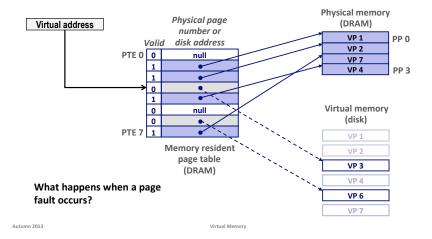

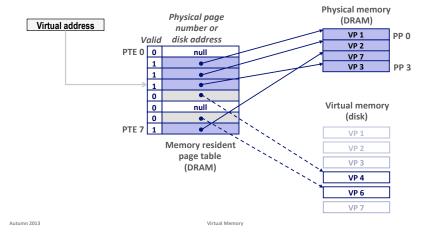

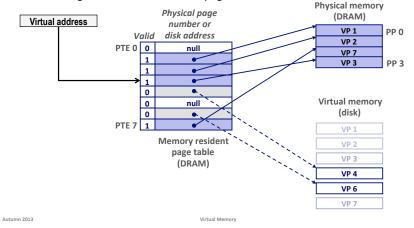

■ A *page table* is an array of *page table entries* (PTEs) that maps virtual pages to physical pages.

University of Washing

## Page Hit

■ Page hit: reference to VM byte that is in physical memory

#### University of Washingto

### **Page Fault**

Page fault: reference to VM byte that is NOT in physical memory

University of Washington

27

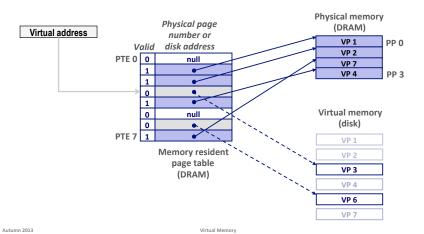

# **Handling Page Fault**

Page miss causes page fault (an exception)

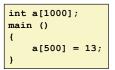

### **Fault Example: Page Fault**

User writes to memory location

80483b7:

That portion (page) of user's memory is currently on disk

\$0xd,0x8049d10

exception: page fault

returns

Create page and load into memory

c7 05 10 9d 04 08 0d

- Page handler must load page into physical memory

- Returns to faulting instruction: mov is executed again!

- Successful on second try

Autumn 2013

Virtual Memory

University of Washin

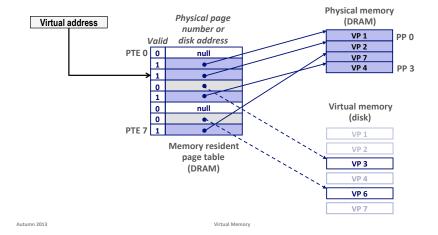

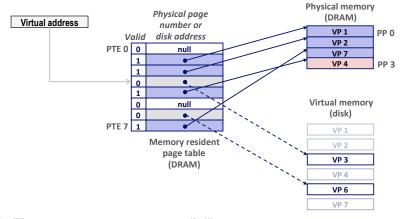

# **Handling Page Fault**

- Page miss causes page fault (an exception)

- Page fault handler selects a victim to be evicted (here VP 4)

# **Handling Page Fault**

- Page miss causes page fault (an exception)

- Page fault handler selects a *victim* to be evicted (here VP 4)

# Why does it work?

### **Handling Page Fault**

- Page miss causes page fault (an exception)

- Page fault handler selects a victim to be evicted (here VP 4)

- Offending instruction is restarted: page hit!

University of Washingt

### Why does VM work on RAM/disk? Locality.

- Virtual memory works well for avoiding disk accesses because of locality

- Same reason that L1 / L2 / L3 caches work

- The set of virtual pages that a program is "actively" accessing at any point in time is called its working set

- Programs with better temporal locality will have smaller working sets

- If (working set size of one process < main memory size):</p>

- Good performance for one process after compulsory misses

- But if

#### SUM(working set sizes of all processes) > main memory size:

- Thrashing: Performance meltdown where pages are swapped (copied) between memory and disk continuously. CPU always waiting or paging.

- Full quote: "Every problem in computer science can be solved by adding another level of indirection, but that usually will create another problem."

Autumn 2013

Virtual Memory

31

Autumn 2013

Virtual Memory

32

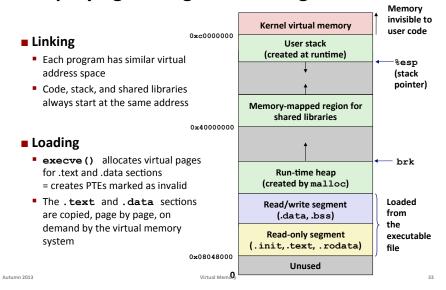

# **Simplifying Linking and Loading**

University of Washingtor

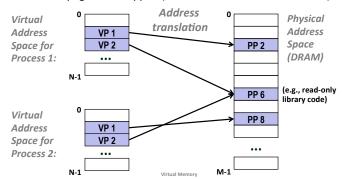

# **VM for Protection and Sharing**

Autumn 2013

- The mapping of VPs to PPs provides a simple mechanism to protect memory and to share memory between processes.

- Sharing: just map virtual pages in separate address spaces to the same physical page (here: PP 6)

- Protection: process simply can't access physical pages to which none of its virtual pages are mapped (here: Process 2 can't access PP 2).

### **VM for Managing Multiple Processes**

- Key abstraction: each process has its own virtual address space

- It can view memory as a simple linear array

- With virtual memory, this simple linear virtual address space need not be contiguous in physical memory

- Process needs to store data in another VP? Just map it to any PP!

University of Washing

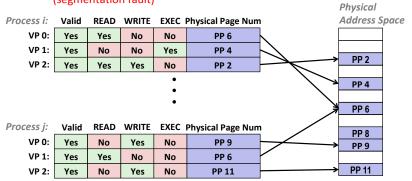

# **Memory Protection Within a Single Process**

Can we use virtual memory to control read/write/execute permissions? How?

# **Memory Protection Within a Single Process**

- Extend page table entries with permission bits

- MMU checks these permission bits on every memory access

- If violated, raises exception and OS sends SIGSEGV signal to process (segmentation fault)

Autumn 2013 Virtual Memory

**University of Washington**

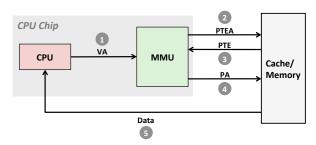

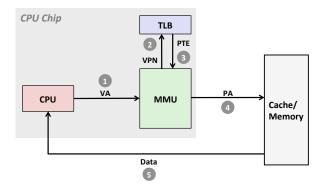

# **Address Translation: Page Hit**

- 1) Processor sends virtual address to MMU (memory management unit)

- 2-3) MMU fetches PTE from page table in cache/memory

- 4) MMU sends physical address to cache/memory

- 5) Cache/memory sends data word to processor

### **Terminology**

#### context switch

Switch between processes on the same CPU

#### page in

Move pages of virtual memory from disk to physical memory

#### page out

Move pages of virtual memory from physical memory to disk

#### thrash

- Total working set size of processes is larger than physical memory

- Most time is spent paging in and out instead of doing useful computation

Autumn 2013 Virtual Memory 38

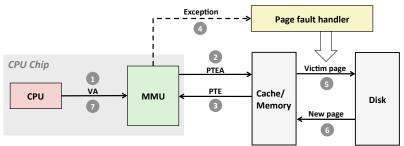

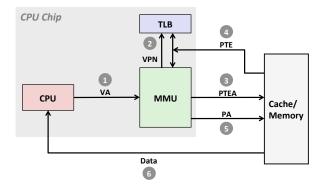

# **Address Translation: Page Fault**

- 1) Processor sends virtual address to MMU

- 2-3) MMU fetches PTE from page table in cache/memory

- 4) Valid bit is zero, so MMU triggers page fault exception

- 5) Handler identifies victim (and, if dirty, pages it out to disk)

- 6) Handler pages in new page and updates PTE in memory

- 7) Handler returns to original process, restarting faulting instruction

Autumn 2013

Virtual Memory

39

Autumn 2013

Virtual Memory

40

### **Hmm... Translation Sounds Slow!**

- The MMU accesses memory *twice*: once to first get the PTE for translation, and then again for the actual memory request from the CPU

- The PTEs may be cached in L1 like any other memory word

- But they may be evicted by other data references

- And a hit in the L1 cache still requires 1-3 cycles

- What can we do to make this faster?

Autumn 2013

Virtual Memory

rv

Autumn 2013

Virtual Memory

....

#### **TLB Hit**

#### A TLB hit eliminates a memory access

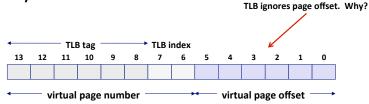

### Speeding up Translation with a TLB

- Solution: add another cache!

- **■** Translation Lookaside Buffer (TLB):

- Small hardware cache in MMU

- Maps virtual page numbers to physical page numbers

- Contains complete page table entries for small number of pages

- Modern Intel processors: 128 or 256 entries in TLB

- Much faster than a page table lookup in cache/memory

**TLB Miss**

A TLB miss incurs an additional memory access (the PTE)

Fortunately, TLB misses are rare. Does a TLB miss require disk access?

Autumn 2013

Virtual Memory

43

Autumn 2013

Virtual Memory

44

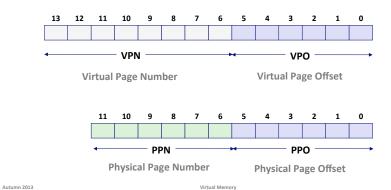

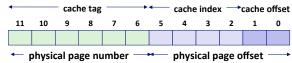

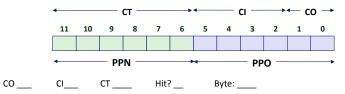

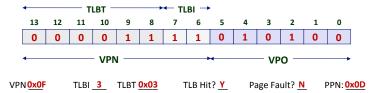

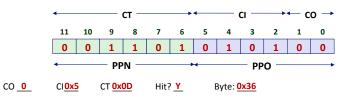

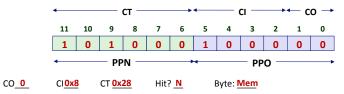

- 14-bit virtual addresses

- 12-bit physical address

- Page size = 64 bytes

University of Washington

# **Simple Memory System TLB**

16 entries

Autumn 2013

4-way associative

| Set | Tag | PPN | Valid |

|-----|-----|-----|-------|-----|-----|-------|-----|-----|-------|-----|-----|-------|

| 0   | 03  | -   | 0     | 09  | 0D  | 1     | 00  | -   | 0     | 07  | 02  | 1     |

| 1   | 03  | 2D  | 1     | 02  | -   | 0     | 04  | -   | 0     | 0A  | -   | 0     |

| 2   | 02  | -   | 0     | 08  | -   | 0     | 06  | -   | 0     | 03  | -   | 0     |

| 3   | 07  | -   | 0     | 03  | 0D  | 1     | 0A  | 34  | 1     | 02  | -   | 0     |

Virtual Memory

**Simple Memory System Page Table**

■ Only showing first 16 entries (out of 256 = 28)

| VPN | PPN | Valid |

|-----|-----|-------|

| 00  | 28  | 1     |

| 01  | _   | 0     |

| 02  | 33  | 1     |

| 03  | 02  | 1     |

| 04  | -   | 0     |

| 05  | 16  | 1     |

| 06  | -   | 0     |

| 07  | -   | 0     |

| VPN | PPN | Valid |

|-----|-----|-------|

| 08  | 13  | 1     |

| 09  | 17  | 1     |

| 0A  | 09  | 1     |

| ОВ  | -   | 0     |

| 0C  | -   | 0     |

| 0D  | 2D  | 1     |

| 0E  | 11  | 1     |

| OF  | 0D  | 1     |

■ What about a real address space? Read more in the book...

Autumn 2013 Virtual Memory

### **Simple Memory System Cache**

- 16 lines, 4-byte block size

- Physically addressed

- Direct mapped

| ldx | Tag | Valid | во | B1 | B2 | В3 | 1 | ldx | Tag | Valid | В0 | B1 | B2 | B. |

|-----|-----|-------|----|----|----|----|---|-----|-----|-------|----|----|----|----|

| 0   | 19  | 1     | 99 | 11 | 23 | 11 |   | 8   | 24  | 1     | 3A | 00 | 51 | 8  |

| 1   | 15  | 0     | -  | -  | -  | -  |   | 9   | 2D  | 0     | -  | -  | -  | -  |

| 2   | 1B  | 1     | 00 | 02 | 04 | 08 |   | Α   | 2D  | 1     | 93 | 15 | DA | 31 |

| 3   | 36  | 0     | -  | -  | -  | -  |   | В   | 0B  | 0     | -  | -  | -  | -  |

| 4   | 32  | 1     | 43 | 6D | 8F | 09 |   | С   | 12  | 0     | -  | -  | -  | -  |

| 5   | 0D  | 1     | 36 | 72 | F0 | 1D |   | D   | 16  | 1     | 04 | 96 | 34 | 1  |

| 6   | 31  | 0     | -  | -  | -  | -  |   | Е   | 13  | 1     | 83 | 77 | 1B | D: |

| 7   | 16  | 1     | 11 | C2 | DF | 03 |   | F   | 14  | 0     | -  | -  | -  | -  |

# **Current state of caches/tables**

#### TLB

| Set | Tag | PPN | Valid |

|-----|-----|-----|-------|-----|-----|-------|-----|-----|-------|-----|-----|-------|

| 0   | 03  | -   | 0     | 09  | 0D  | 1     | 00  | -   | 0     | 07  | 02  | 1     |

| 1   | 03  | 2D  | 1     | 02  | -   | 0     | 04  | -   | 0     | 0A  | -   | 0     |

| 2   | 02  | -   | 0     | 08  | -   | 0     | 06  | -   | 0     | 03  | -   | 0     |

| 3   | 07  | -   | 0     | 03  | 0D  | 1     | 0A  | 34  | 1     | 02  | -   | 0     |

| VPN | PPN | Valid | VPN | PPN | Valid |

|-----|-----|-------|-----|-----|-------|

| 00  | 28  | 1     | 08  | 13  | 1     |

| 01  | -   | 0     | 09  | 17  | 1     |

| 02  | 33  | 1     | 0A  | 09  | 1     |

| 03  | 02  | 1     | ОВ  | -   | 0     |

| 04  | -   | 0     | 0C  | -   | 0     |

| 05  | 16  | 1     | 0D  | 2D  | 1     |

| 06  | -   | 0     | 0E  | 11  | 1     |

| 07  | -   | 0     | OF  | 0D  | 1     |

Page table

#### Cache

| ldx | Tag | Valid | В0 | B1 | В2 | В3 |   | ldx | Tag | Valid | В0 | B1 | В2 | В3 |

|-----|-----|-------|----|----|----|----|---|-----|-----|-------|----|----|----|----|

| 0   | 19  | 1     | 99 | 11 | 23 | 11 |   | 8   | 24  | 1     | 3A | 00 | 51 | 89 |

| 1   | 15  | 0     | -  | -  | -  | -  |   | 9   | 2D  | 0     | -  | -  | -  | -  |

| 2   | 1B  | 1     | 00 | 02 | 04 | 08 |   | Α   | 2D  | 1     | 93 | 15 | DA | 3B |

| 3   | 36  | 0     | -  | -  | -  | -  |   | В   | 0B  | 0     | -  | -  | -  | -  |

| 4   | 32  | 1     | 43 | 6D | 8F | 09 |   | С   | 12  | 0     | -  | -  | -  | -  |

| 5   | 0D  | 1     | 36 | 72 | F0 | 1D | П | D   | 16  | 1     | 04 | 96 | 34 | 15 |

| 6   | 31  | 0     | -  | -  | -  | -  |   | Е   | 13  | 1     | 83 | 77 | 1B | D3 |

| 7   | 16  | 1     | 11 | C2 | DF | 03 |   | F   | 14  | 0     | -  | -  | -  | -  |

Autumn 2013 Virtual Memory

University of Washington

### **Address Translation Example #2**

Virtual Address: 0x0B8F

#### **Physical Address**

### **Address Translation Example #1**

Virtual Address: 0x03D4

#### **Physical Address**

Autumn 2013 Virtual Memory

University of Washing

# **Address Translation Example #3**

Virtual Address: 0x0020

#### **Physical Address**

Autumn 2013

Virtual Memory

51

Autumn 2013

Virtual Memory

55

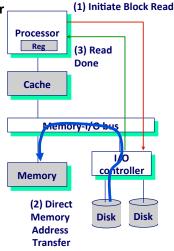

### **Servicing a Page Fault**

(1) Processor signals disk controller

Read block of length P starting at disk address X

Store starting at memory address Y

#### (2) Read occurs

- Direct Memory Access (DMA)

- Under control of I/O controller

#### ■ (3) Controller signals completion

- Interrupts processor

- OS resumes suspended process

Autumn 2013 Virtual Memory

### **Memory System Summary**

#### L1/L2 Memory Cache

- Purely a speed-up technique

- Behavior invisible to application programmer and (mostly) OS

- Implemented totally in hardware

#### Virtual Memory

- Supports many OS-related functions

- Process creation, task switching, protection

- Operating System (software)

- Allocates/shares physical memory among processes

- Maintains high-level tables tracking memory type, source, sharing

- Handles exceptions, fills in hardware-defined mapping tables

- Hardware

- Translates virtual addresses via mapping tables, enforcing permissions

- Accelerates mapping via translation cache (TLB)

#### Summary

#### Programmer's view of virtual memory

- Each process has its own private linear address space

- Cannot be corrupted by other processes

#### System view of virtual memory

- Uses memory efficiently by caching virtual memory pages

- Efficient only because of locality

- Simplifies memory management and sharing

- Simplifies protection by providing a convenient interpositioning point to check permissions

Autumn 2013 Virtual Memory 54

### **Memory System Summary**

#### L1/L2 Memory Cache

- Controlled by hardware

- Programmer cannot control it

- Programmer can write code in a way that takes advantage of it

#### Virtual Memory

- Controlled by OS and hardware

- Programmer cannot control mapping to physical memory

- Programmer can control sharing and some protection

- via OS functions (not in 351)

Autumn 2013 Virtual Memory 55 Autumn 2013 Virtual Memory